今更聞けない無線と回路設計の話

【テーマ1】三角関数のかけ算と無線工学

第19話

ループフィルタとPLLの応答特性の話(その4)

2023年9月1日掲載

第18話では、一般に使用されているPLLが二次以上の高次ループとなること、ならびに高次ループはそのままでは不安定(発振する)であり、ループフィルタを挿入して極の周波数(固有角周波数ωn)の位相余裕を確保する必要があることを解説しました。PLLのループ設計を行う上で基本的に押さえておかなければならない箇所は概ねお伝えしたのですが、昨今主流の定電流型チャージポンプの場合、電流-電圧変換の為のキャパシタCPをパッシブリードフィルタに置き換えて設計する事例が一般的ですので、第19話はこのあたりのお話からスタートです。

1. パッシブリードフィルタ

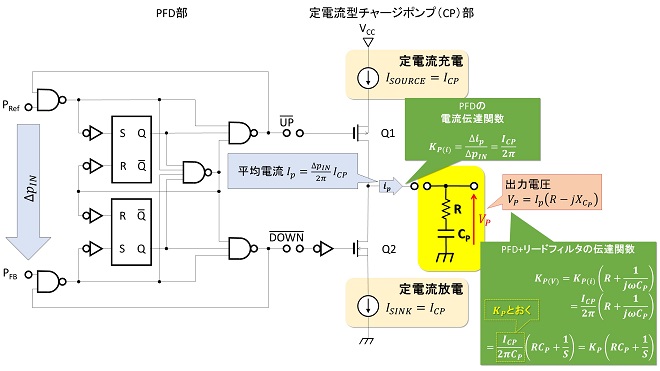

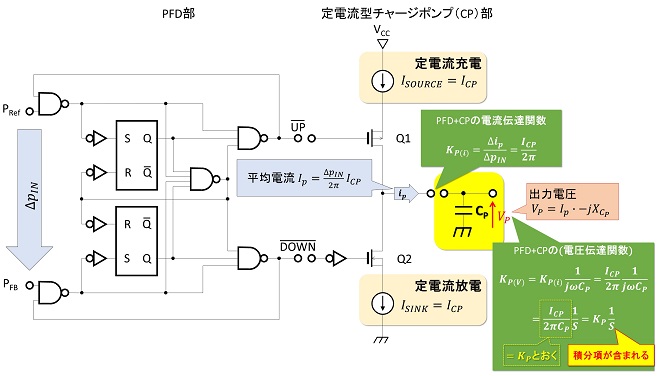

図1は第18話の図1を再掲したものです。定電流型チャージポンプ(位相差に比例した電流値が出力されるチャージポンプ)から位相差に比例した電圧を取り出す為には、チャージポンプ出力にキャパシタCP(図中、黄色く示した部分)を接続して電流電圧変換を行う必要がありました。

図1 定電流型チャージポンプ方式位相検波器(第18話の図1を再掲)

パッシブリードフィルタとは、図2に示すように、このCPに直列に抵抗Rを接続したものです。見た目、第18話の図5で解説したラグリードフィルタに似ています。

この回路は機能上「フィルタ」と呼びますが、実際にはRとCPだけでは伝達関数を定義できず、位相検波器の出力特性を補正していると考えた方が理解しやすいと思います。図2の吹き出しに示すとおり、伝達関数もループフィルタとして独立した関数F (S )ではなく、位相検波器の伝達関数KP (V )として定義されます。動作を理解する為、図1、図2のチャージポンプ部分を定電流源に置き換えたのが図3です。

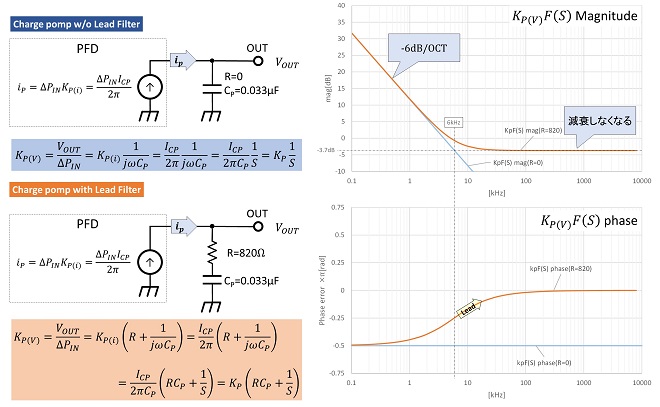

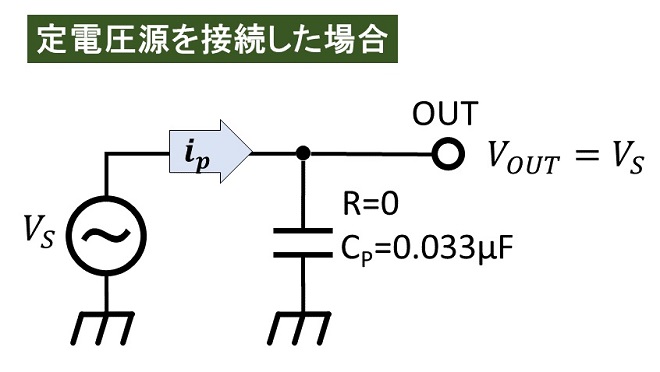

まずCPのみの場合を見てみましょう。図3Bに示すように、定電圧源VS の出力端子にキャパシタCPを接続した場合、OUT端子の電圧振幅も電圧位相も周波数に関係なく定電圧源VS と同じ値になり、CPに流れる電流ip の位相が電圧位相よりも90°進みます。

図3B

これに対して図3のように定電流源に接続した場合は、OUT端子の電圧VOUT はキャパシタのリアクタンスに比例するので振幅は電源周波数𝑓の逆数に比例、位相は電流源の位相を基準に出力電圧(CPの端子電圧)の位相を測る事になるので、第18話で解説したとおり、電源周波数𝑓に関係なく常に90°遅延となります。(図3の水色のグラフ)※1

これに対してCPに直列に抵抗Rを挿入したときのOUT端子の電圧VOUT は、電源が定電流源なのでRの端子線圧は一定の値となり、CPの端子電圧のみ周波数で変化します。この結果、図3のオレンジのグラフに示すように、周波数が低くR ≪ |XCp |と見なせる領域ではCPのみの場合と同じ特性を示し、周波数が高くR ≫ |XCp |なってとなる領域では、VOUT =ip ∙ Rに漸近し、位相は電流源と同相(つまり0°遅延)に漸近します。CPに直列にRを接続した時は、R ≫ |XCp |となる周波数領域で減衰特性が失われる代わりに、その直前の周波数領域で位相進み特性(Lead特性)を獲得することができます。

※1: 定電流源については第10話で詳しく解説していますので参考にしてください。

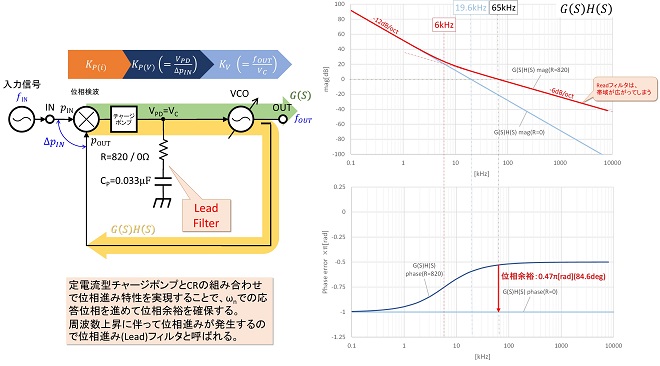

2. リードフィルタを用いたPLLの設計

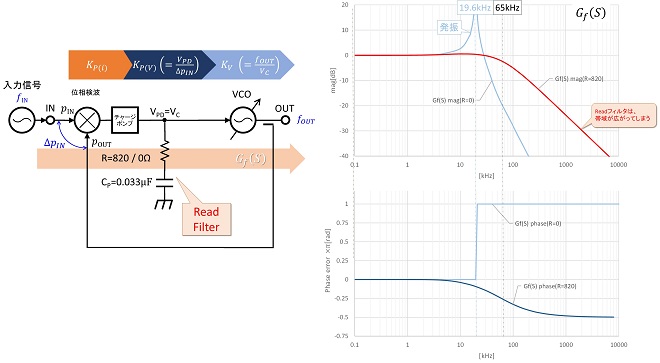

では第18話で題材にしたPLL(第18話の図3、図4参照)をパッシブリードフィルタで安定化させてみましょう。位相検波器の伝達関数KP (i ) とVCOの伝達関数KV は第18話の図3と同じです。ここではCPを第18話と同じ0.033μFとし、直列抵抗Rに820Ωを適用します。この時の位相検波器の伝達関数(フィルタの伝達関数を含む)KP (V )F (S )は、図3のオレンジのグラフに示した通りとなります。この時の一巡伝達関数を図4に示します。

図中、水色のグラフはR=0Ω、すなわち直列Rを挿入しないの時の特性で、第18話の図3と同じ結果を示しています。この時のループのωn(一巡伝達関数の振幅が0dBになる角周波数)は123.15krad/sec(19.6kHz)でした。直列に820Ωを挿入すると、図3に示すように位相検波器の伝達関数が-6dB/octの高域減衰特性から6kHz付近を境に定利得特定に移行します。この結果、一巡伝達関数の振幅特性は図4の赤のグラフの特性となり、6kHz付近を境に高域減衰特性が-12dB/octから-6dB/octに変化します。この結果、ωnは利得の上昇に伴って65kHzに上昇しました。同様に位相特性も-π[rad]から-π/2[rad]に漸近していきます。この結果、0.47π[rad](84.6°)の位相余裕が確保できました。ちなみに第18話で解説したラグフィルタによるループの安定化設計では、高域減衰特性が-12dB/octから-18dB/octに変化して利得が下がった結果、ωnも低い周波数にシフトしました(第18話の図7)。これとは逆パタンの設計です。

続いて、閉ループ伝達関数Gf (S )を図5に示します。

図5 パッシブリードフィルタを用いたPLLの閉ループ伝達関数

図4と同様、水色のグラフはR=0Ωの時の特性を示しています。R=0Ωの時には位相余裕が0°だったので、ωnでGf (S )が発散して発振を示唆する結果になっていましたが、直列Rを挿入することで位相余裕を確保した結果、図5赤色のグラフに示すとおり、Gf (S )の発散は解消しています。但しωnが上昇し、一巡伝達関数の高域減衰量が小さくなった結果、ループの通過帯域幅は広がる結果になっており、第18話のラグフィルタとは逆の関係になっています。

3. ラグ・リード特性を与えたPLLの設計

以上解説の通り、定電流型チャージポンプを搭載したPLL-ICとリードフィルタを用いたPLLは通過帯域(応答周波数帯域)を広く確保する事ができます。これは第14話で解説した周波数シンセサイザ(雑音のないリファレンスにVCOを同期させるPLL)を設計する上で有利な特性と言えます。しかしチャージポンプ方式の位相検波器の出力は、定電流方式/定電圧方式にかかわらず、位相比較周波数と同一周期のパルス波であり、後段のキャパシタ・・・ すなわちループフィルタで平滑する必要があります。これはループの通過帯域を比較周波数よりも狭く設計する必要があることを示唆しています。チャージポンプ出力電圧の平滑が不十分な場合、リファレンスリークと云って、VCOの出力信号が比較周波数で変調された状態になります(図6)。

図6 リファレンスリーク、ならびにループ帯域とPLLの出力雑音の関係

図6はPLLの入力波形と出力波形の関係を示したものです。

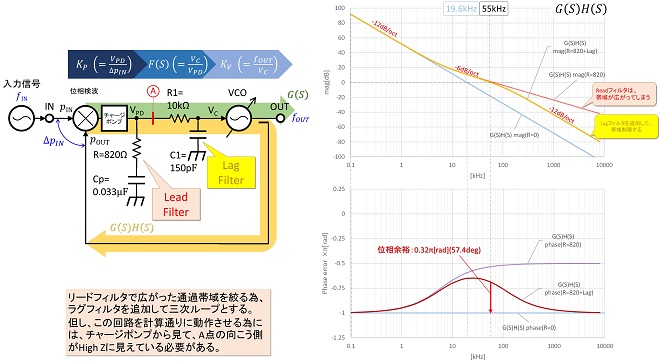

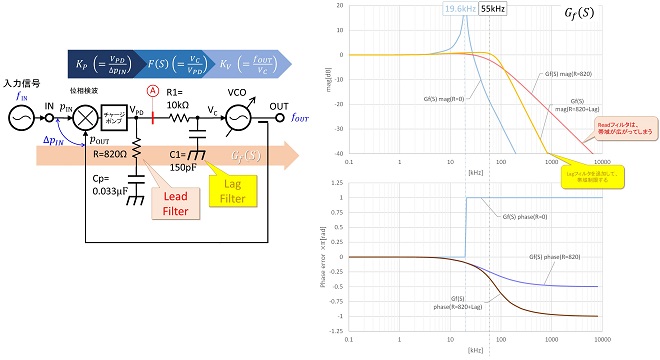

PLL出力の位相雑音※2レベルを下げるためには、ループフィルタの帯域(一巡伝達関数(利得)が0dB以上の帯域)を広くとって、閉ループ伝達関数(利得)が0dBとなる帯域を広く確保する事が重要ですが、位相比較周波数(図6ではfIN )を超えて帯域を確保しようとすると、リファレンスリークスプリアスが強く発生してしまいます。このため、必要以上に広がりすぎた閉ループ伝達関数Gf (S )を絞る為、ラグフィルタを追加する設計がよく採用されます。図7、図8は、図4、図5で解説した設計事例にカットオフ周波数≒100kHz(第18話の図5に示した伝達関数が-3dBとなる周波数)のラグフィルタを挿入した例です。このPLLはラグフィルタを追加することで三次ループとなります。

ラグフィルタを挿入することで一巡伝達関数G (S )H (S )(振幅特性)は図7の赤のグラフからオレンジのグラフになり、一旦-6dB/octとなっていた傾きは100kHz付近を境に再び-12dB/octになります。この結果ωnは少し下がって55kHzになりました。位相特性は紫のグラフから茶色のグラフとなり、位相遅れ(ラグ)特性が付加されていることが判ります。ラグ特性を追加した結果、位相余裕は84.6°から57.4°に減少しています。

図8 ラグフィルタを追加した三次ループPLLの閉ループ伝達関数

これに伴い、閉ループ利得Gf (S )の振幅特性も図8の赤のグラフからオレンジのグラフに変化し、100kHzより高域の減衰特性が改善している事がわかります。一方で位相余裕が減少した影響は55kHz付近の振幅利得が0dBをやや超えていて、不足制動の傾向になっていることから確認できます。従って、このPLLは入力位相をステップで変化させるとオーバシュートが出やすいと予想されます。シンセサイザなどの用途で周波数を連続的に切り替えたときに、受信周波数がシームレスで切り替わるようにする為には、ラグフィルタのカットオフ周波数をもう少し高くとって、位相余裕を確保するべきかもしれません。但しリファレンスリークスプリアスレベルとのトレードオフになるので、比較周波数を何Hzにするかも含め、設計者の腕の見せ所となります。

※2: 位相雑音については第13話で解説しました。

4. 第19話のまとめ

第19話では定電流型チャージポンプを搭載したPLL-ICにおけるループフィルタの構成方法について解説しました。以下第19話の要点です。

- ・定電流型チャージポンプを搭載するPLLーICにおいては、定電流源で駆動されて電圧を出力するパッシブリードフィルタを用いて位相補償を行うのが一般的である。

- ・チャージポンプ式位相検波器は、位相比較周波数の周期で出力されるパルスを平滑して位相比較電圧を得る為、位相比較周波数のn倍波成分(nは整数)が含まれる。これをリファレンスリークと呼び、ループフィルタでの減衰(平滑)が不十分だとVCO出力と掛け算されて出力信号にスプリアスとして流出する。

- ・パッシブリードフィルタは、電圧駆動・電圧出力型のパッシブラグリードフィルタと同様、位相進みの特性を得られる代わりに、高域減衰特性が劣化する。ループ安定を確保するだけならこれで問題ないが、閉ループ伝達関数の通過帯域を制限する必要がある場合は、ラグフィルタを追加して減衰特性を補う必要がある。

- ・閉ループ伝達関数の通過帯域はPLL出力の雑音特性に強く影響する。シンセサイザなど、CNRが高い入力信号(綺麗な信号)の場合は、帯域を広く採るほど出力のCNRは改善するが、比較周波数を超えてしまうとリファレンスリークが強く出てしまう。ジッタアッテネータなど入力信号のCNRが低い場合は逆に帯域を絞る設計を行う。 → 第14話参照

- ・スプリアスを落とす為に追加するラグフィルタは、カットオフ周波数がリードフィルタの位相補償周波数に近づき過ぎると、ωnの低下やリードフィルタの位相補償量低下による位相余裕不足を起こす。

- ・位相余裕が不足すると周波数切り替えなどを行った時にPLL出力がオーバシュートやリンギングを起こしやすくなり、用途によっては問題になる。

かつて(私が現役の頃)は定電圧出力のPLL-ICが主流で、一部のメーカのみ定電流型のチャージポンプを採用していました。従って教科書に登場するループフィルタは第18話で解説したラグリードフィルタで位相進み補償を行って位相余裕を確保し、高域減衰特性の劣化をラグフィルタで補うという設計スタイルばかりでした。大学の授業でも、まだ定電圧型のチャージポンプ(位相検波器が位相差に比例した電圧を出力する)を前提とした解説が主流なのではないでしょうか。現在では定電流型のチャージポンプが主流だと思いますので、教科書や巷のHow to本で独学される方は、そのあたりの違いを意識して勉強されることをお勧めします。

ちなみに今回、図7、図8で解説した回路はチャージポンプの定電流出力をLeadフィルタで電圧に変換し、電圧入力のラグフィルタで高域応答を絞る設計になっています。従って、チャージポンプ(Leadフィルタ)からVCO側(図7、8のA点から右側の回路)がハイインピーダンスに見えていないと、計算通りの特性にはなりません。このため定電流型チャージポンプを使用したPLLでは、ラグフィルタについても定電流源に対応した回路で設計されることが多くなっています。

今回、まとめて解説しようと考えていましたが、ボリウムがありすぎて力尽きてしまいました。次回は、このあたりからお話を始めたいと考えます。

第19話の執筆には下記文献を参考にさせて頂きました。

トランジスタ技術増刊 RFワールド No20 特集「PLLシンセサイザの実用設計法」(小宮 浩著) 2012年11月 CQ出版社

今更聞けない無線と回路設計の話 バックナンバー

- 【テーマ2】デシベルと無線工学 (第19話) レベルダイヤグラムの縦軸(その3)

- 【テーマ2】デシベルと無線工学 (第18話) レベルダイヤグラムの縦軸(その2)

- 【テーマ2】デシベルと無線工学 (第17話) レベルダイヤグラムの縦軸(その1)

- 【テーマ2】デシベルと無線工学 (第16話) レベルダイヤグラムの構成

- 【テーマ2】デシベルと無線工学 (第15話) 非線形歪み(その5)

- 【テーマ2】デシベルと無線工学 (第14話) 非線形歪み(その4)

- 【テーマ2】デシベルと無線工学 (第13話) 非線形歪み(その3)

- 【テーマ2】デシベルと無線工学 (第12話) 非線形歪み(その2)

- 【テーマ2】デシベルと無線工学 (第11話) 非線形歪み(その1)

- 【テーマ2】デシベルと無線工学 (第10話) 線形歪み(フェージング現象)

- 【テーマ2】デシベルと無線工学 (第9話) 足される雑音と掛けられる雑音

- 【テーマ2】デシベルと無線工学 (第8話) 等価雑音の内訳

- 【テーマ2】デシベルと無線工学 (第7話) 無線通信の成立条件(その3)

- 【テーマ2】デシベルと無線工学 (第6話) 無線通信の成立条件(その2)

- 【テーマ2】デシベルと無線工学 (第5話) 無線通信の成立条件

- 【テーマ2】デシベルと無線工学 (第4話) dBmとdBµVの複雑な関係

- 【テーマ2】デシベルと無線工学 (第3話) dB(デシベル)を知る(その2)

- 【テーマ2】デシベルと無線工学 (第2話) dB(デシベル)を知る(その1)

- 【テーマ2】デシベルと無線工学 (第1話) (プロローグ)無線通信機の天井と床

- 【テーマ1】三角関数のかけ算と無線工学 (第30話) 三角関数のかけ算と無線工学の切っても切れない深い縁

- 【テーマ1】三角関数のかけ算と無線工学 (第29話) 交流ベクトル空間と直交ミキサ(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第28話) 交流ベクトル空間と直交ミキサ(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第27話) 交流ベクトル空間と直交ミキサ(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第26話) 交流ベクトル空間と直交ミキサ

- 【テーマ1】三角関数のかけ算と無線工学 (第25話) マイナスの周波数

- 【テーマ1】三角関数のかけ算と無線工学 (第24話) 同一周波数のサイン波の掛け算と周波数の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第23話) 同一周波数のサイン波の掛け算と周波数の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第22話) 同一周波数のサイン波の掛け算と周波数の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第21話) ループフィルタとPLLの応答特性の話(その6)

- 【テーマ1】三角関数のかけ算と無線工学 (第20話) ループフィルタとPLLの応答特性の話(その5)

- 【テーマ1】三角関数のかけ算と無線工学 (第19話) ループフィルタとPLLの応答特性の話(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第18話) ループフィルタとPLLの応答特性の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第17話) ループフィルタとPLLの応答特性の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第16話) ループフィルタとPLLの応答特性の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第15話) 位相検波器の話

- 【テーマ1】三角関数のかけ算と無線工学 (第14話) PLLの動作原理と代表構成

- 【テーマ1】三角関数のかけ算と無線工学 (第13話) PLLの役割とサイン波の純度について

- 【テーマ1】三角関数のかけ算と無線工学 (第12話) 同一周波数のサイン波のかけ算と位相のはなし

- 【テーマ1】三角関数のかけ算と無線工学 (第11話) ギルバートセル乗算器(その3・ギルバートセル乗算回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第10話) ギルバートセル乗算器(その2・定電流源とカレントミラー回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第9話) ギルバートセル乗算器(その1・差動増幅の基礎)

- 【テーマ1】三角関数のかけ算と無線工学 (第8話) ダブルバランスドミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第7話) ダブルバランスドミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第6話) トランジスタミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第5話) トランジスタミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第4話) 非線形動作を利用したかけ算のまとめ

- 【テーマ1】三角関数のかけ算と無線工学 (第3話) ミキサの線形性って何?

- 【テーマ1】三角関数のかけ算と無線工学 (第2話) 周波数変換とミキサ(混合)回路

- 【テーマ1】三角関数のかけ算と無線工学 (第1話) サイン波のかけ算

外部リンク

アマチュア無線関連機関/団体

各総合通信局/総合通信事務所

アマチュア無線機器メーカー(JAIA会員)