今更聞けない無線と回路設計の話

【テーマ1】三角関数のかけ算と無線工学

第9話 ギルバートセル乗算器(その1・差動増幅の基礎)

第7話から第8話にかけて、ダイオードミキサの代表ともいえるDBMについて表計算と回路シミュレータを用いて解説しました。IC化されていない送受信機の周波数変換回路は、殆どがこれまで解説したトランジスタミキサやDBMで実現されています。一方で高周波回路のIC化が進み、周波数変換回路もSiGeやCMOSプロセスによる高周波LSIやアナログASICに取り込まれるようになってきました。CMOSに代表されるモノリシックICは、DBMに使用されるトランスの実現が困難なため、差動増幅器ベースの乗算回路が多用されます。第9話からはその代表回路ともいえる「ギルバートセル」乗算回路について解説します。

1. ギルバートセルとは

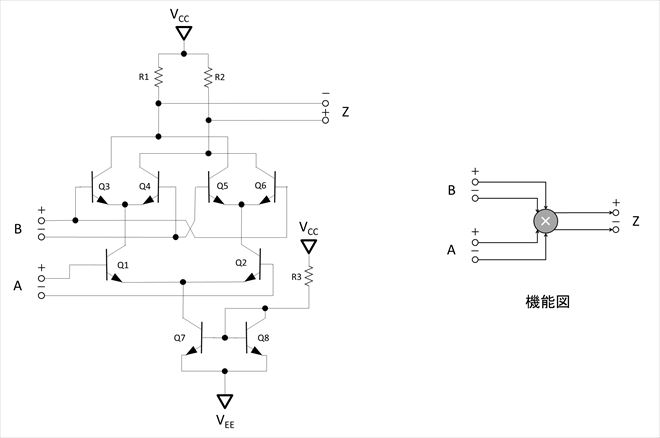

ギルバートセルとは、2020年に亡くなられたアナログ・デバイセズ社の技術フェロー バリー・ギルバート博士※1が考案したとされるアナログ乗算回路です。図1に示す通り、差動増幅器をカスケードに組み合わせた回路構成になっています。これまで解説したトランジスタミキサやダイオードミキサは周波数変換を行うことが主目的であり、2つの信号の乗算精度には着目していませんでした(「ミキサ」と呼ばれる所以です)が、ギルバートセル乗算器は乗算精度が保証された4象限乗算※2が可能な回路です。

図1 ギルバートセル型乗算回路

基本的にICの一部に使用されている回路なので、装置レベルの回路設計者が直接この回路に触れる機会は少ないですが、AD633(ADI)、MC1496(ON Semiconductor)など、二重平衡変調器IC、または乗算器ICとして単機能のICも存在します。(昔はNECからμPA101という乗算回路構成のトランジスタアレーも販売されていました)

2. ギルバートセル乗算器の構成

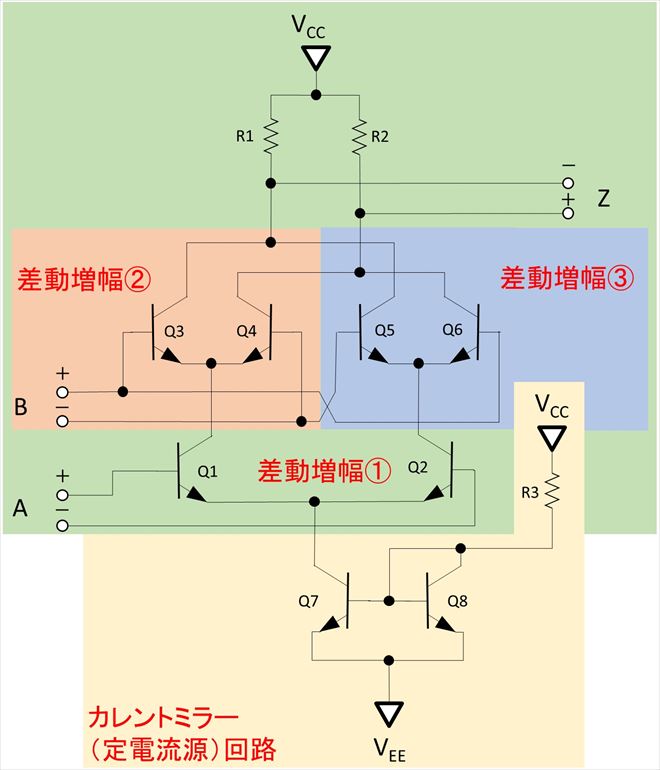

図1の回路をぱっと見るとトランジスタが8個も使用されていて、非常に複雑な回路に見えます。この回路の構成を少し判りやすくする為に色づけしたのが図2です。ギルバートセル乗算器は3つの差動増幅回路と1つのカレントミラー(定電流源)回路から構成されており、A入力を増幅する差動増幅①の2つの出力部にB入力を増幅する差動増幅②と③がそれぞれ縦積み(カスコード接続)された構成となっています。

図2 ギルバートセル型乗算回路の構成

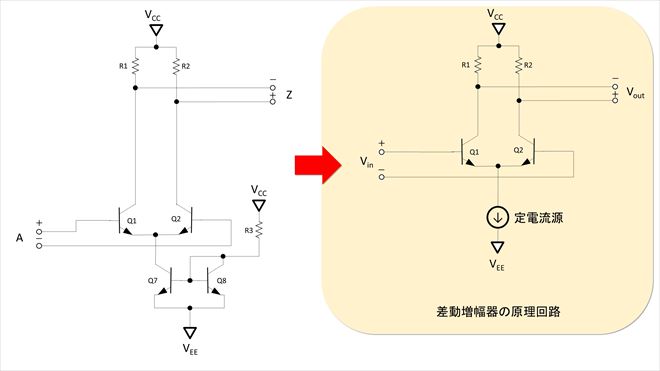

差動増幅器を縦積みする事で乗算の機能を実現しているわけですが、その動作を理解する為には、まず差動増幅回路を理解する必要があります。図2の回路から「差動増幅②」と「差動増幅③」をなくして「差動増幅①」のみとしたのが図3の左側になります。このうちQ7とQ8はカレントミラー回路と呼ばれる回路で定電流源(端子電圧を変化させても流れる電流が変化しない回路)として動作します。従ってこれを定電流源のシンボルに置き換えたのが図3の右側の回路になり、一般に差動増幅回路とは図3の右側の回路全体(トランジスタペアと定電流源)を示します。

図3 ギルバートセル型乗算回路から差動増幅①のみ分離する

3. 差動増幅回路の動作

差動増幅回路とは、その名の通り、2つある入力端子の電圧差(Vin)に比例した電圧(Vout)を出力する増幅回路です。先に述べたとおり、基本的な差動増幅回路は図3の右側の図に示すような構成になっていて、入力信号は+/−別々のトランジスタQ1、Q2のベース端子に接続され、各トランジスタのコレクタ電圧の差分を出力として取り出します。2つのトランジスタの特性は完全に一致している前提です。出力電圧を取り出す為の抵抗R1とR2も通常は同じ値を選択します。+入力を増幅するトランジスタQ1と−入力を増幅するトランジスタQ2の各エミッタが共通の定電流源を介してVEE(-電源)に接続されています。ここまでの解説だけだと、差動増幅回路とは、差動信号を増幅する為に特性の揃った2つのトランジスタを使用して、+/−それぞれの信号を別々の信号として増幅して、その出力の差分を差動出力として取り出している・・・ ようにも見えますが、2つのトランジスタのエミッタを共通回路にしているところが差動増幅回路とバラバラの増幅回路との大きな相違点になります。以下、エミッタを共通回路にして定電流源に接続する事でどのような動作になるのか、図を使って解説します。

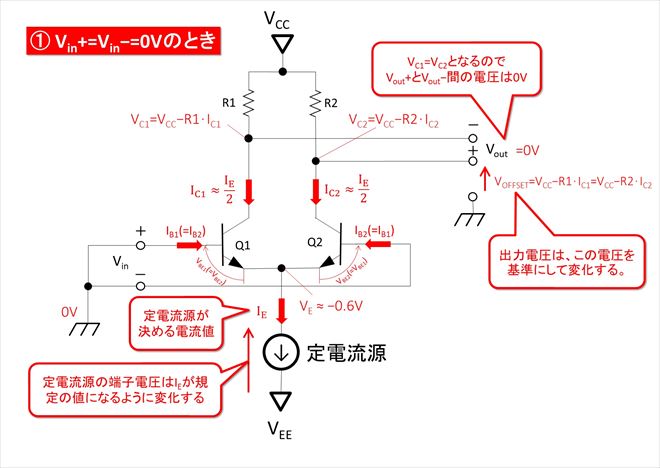

(1) 無信号(Vin+=Vin-=0V)のとき

図4に入力電圧が0V(コモンモードでもノーマルモードでも0V)※3の時の動作を示します。差動増幅回路ではエミッタが共通回路になっていて、かつ定電流源に接続されるので、Q1、Q2のエミッタ電流の合計値IEは、Q1、Q2の動作状態に関係なく一定の値になります。別の表現をすると、定電流回路は決められたIEになるように、自身の端子電圧=Q1、Q2のエミッタ電圧VEを増減してそれぞれのベース電流IB1、IB2を調整するような動作をします。具体的に書くと、IEが増加するとVEを上昇させてVBE1、VBE2を減少(IB1、IB2が減少)、IEが減少するとVEを下降させてVBE1、VBE2を増加(IB1、IB2が増加)させる事で一定値を保とうとします。

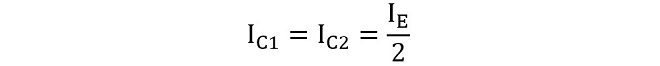

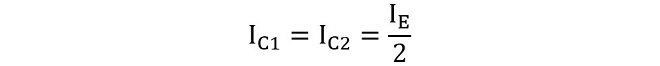

ここから先は話を簡単にするために、各トランジスタのhFEが充分に大きくベース電流IB1≒0、IB2≒0と見なす事ができるとします。IEが一定に保たれる事で、各トランジスタのコレクタ電流IC1、IC2の総和も、IEと同じ値になります。

図4においては、Vin+、Vin− 共に0V。つまりコモンモード電圧0V、ノーマルモード電圧も0Vの状態ですので、Q1、Q2がシリコントランジスタであればVE≈−0.6V、Q1とQ2はエミッタが同じ定電流源に接続されているのでVBE1=VBE2。かつ全く同じ特性なのでIB1=IB2となり、

(式3-1)

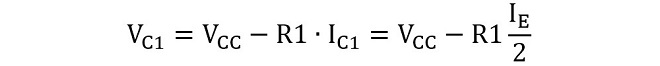

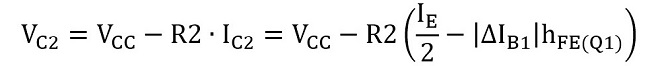

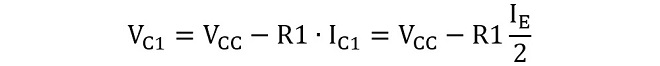

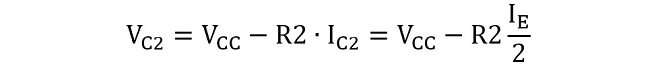

となります。この時の出力電圧は+電源VCCの値から、R1、R2の電圧降下分を引いた値で、

(式3-2)

(式3-3)

となります。先に述べた通りR1=R2なので、VC1=VC2すなわちコモンモード電圧VOFFSETがVC1(=VC2)[V]、ノーマルモード電圧(差動電圧)VOUTが0[V]となります。

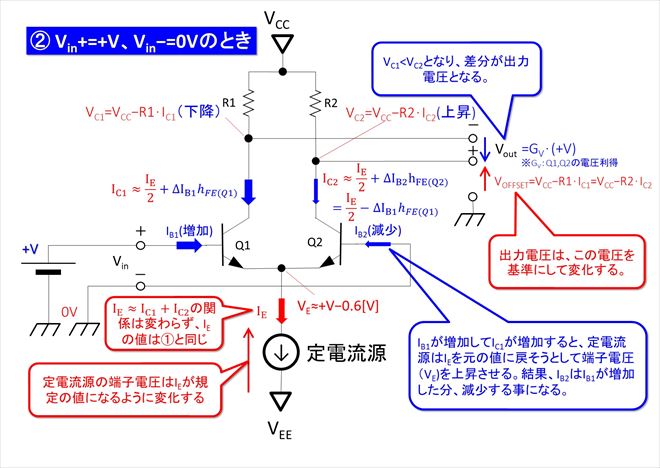

(2) Vin+=+V、Vin-=0Vのとき

Vin+端子に+V[V]、Vin−端子に0[V]の入力電圧が加わった時の回路各部の電圧・電流は図5のようになります。

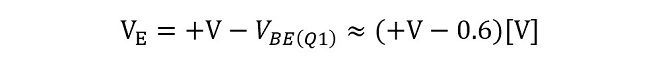

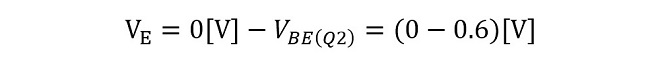

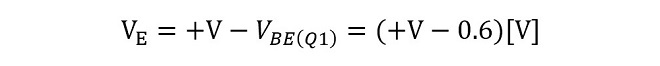

図5ではコモンモード電圧=0[V]、ノーマルモード電圧Vin=+V[V]の状態ですので、Q1のベース電流IB1が増加しようとします。定電流源を負荷抵抗と見なすとQ1のエミッタ側は所謂エミッタフォロワ回路的な動作をするので、エミッタ電圧VEはIB1の増加に伴い、

(式3-4)

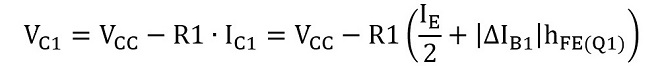

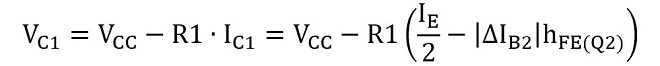

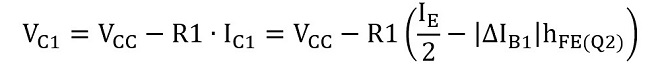

付近まで上昇します。「付近」と書いたのは、Q1のエミッタにはQ2のエミッタも接続され、かつ定電流回路が接続されている為です。VEが(+V−0.6)[V]まで上昇するということは、等価的にQ2のベースに−V[V]の電圧が印加された事になるため、VBE2は減少し、IB2も減少してIC2は減少します。さらにエミッタの定電流源がIEの値(=IC1+IC2)を一定値に維持しようとするので、最終的に

(式3-5)

(式3-6)

となります※4。結果、VOFFSETを基準電圧(コモンモード電圧)として、VC1が-、VC2が+の電圧を出力します。

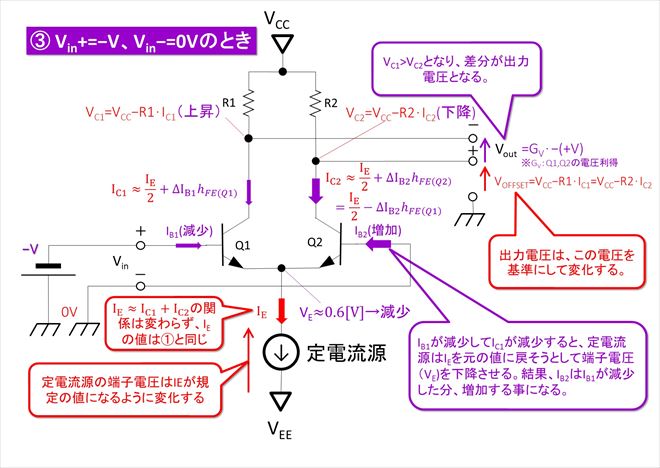

(3) Vin+=−V、Vin-=0Vのとき

Vin+端子に−V[V]、Vin−端子に0[V]の入力電圧が加わった時の回路各部の電圧・電流は図6のようになります。

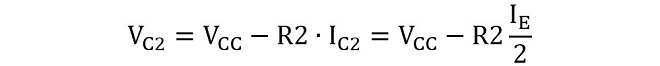

図6ではコモンモード電圧=0V、ノーマルモード電圧Vin=−V[V]の状態ですので、Q1のベース電流IB1が減少しようとします。Q1のエミッタ電圧は0V以下に下がろうとしますが、Q2のベース電圧が0Vなので、エミッタ電圧VEはQ2の電位に縛られ、

(式3-7)

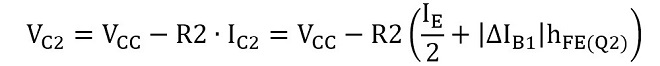

付近から大きく変化しません。但しエミッタの定電流源がIEの値(=IC1+IC2)を一定値に維持しようとするので、IC2を上昇させるために−0.6Vより少し下がったところに落ち着き、コレクタ電圧は

(式3-8)

(式3-9)

となります※4。結果、VOFFSETを基準電圧(コモンモード電圧)として、VC1が+、VC2が-の電圧を出力します。

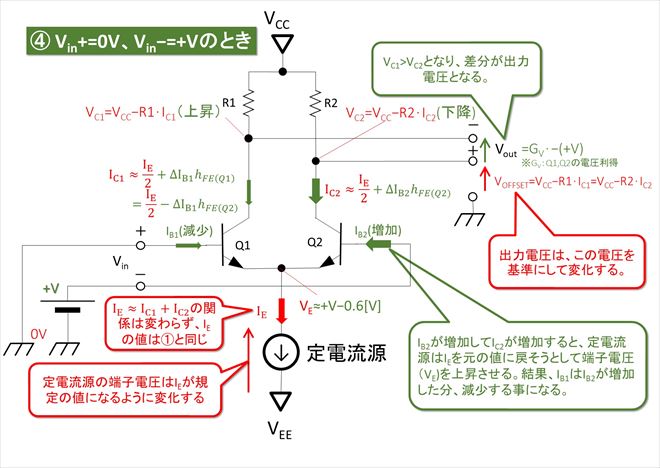

(4) Vin+=0V、Vin-=+Vのとき

Vin+端子に0[V]、Vin−端子に+V[V]の入力電圧が加わった時の回路各部の電圧・電流は図7のようになります。

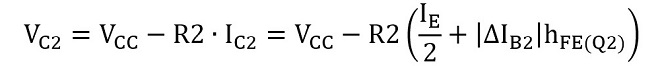

図7は(2)の時とQ1とQ2の電圧・電流関係が逆になるパターンでありVEは

(式3-10)

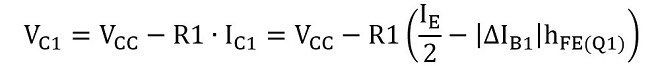

VC1とVC2は

(式3-11)

(式3-12)

となります※4。結果、VOFFSETを基準電圧(コモンモード電圧)として、VC1が-、VC2が+の電圧を出力することとなり、VEの値は異なりますがVC1とVC2は(3)と同じ結果になります。

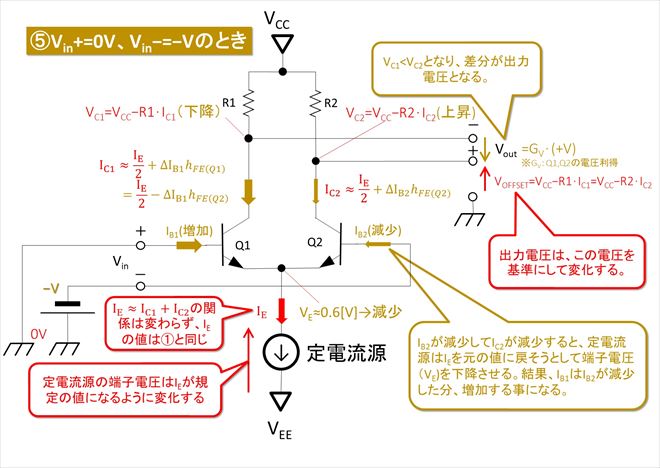

(5) Vin+=0V、Vin-=−Vのとき

Vin+端子に0[V]、Vin−端子に−V[V]の入力電圧が加わった時の回路各部の電圧・電流は図8のようになります。

図8は(4)の時とQ1とQ2の電圧・電流関係が逆になるパターンでありVEは

(式3-13)

VC1とVC2は

(式3-14)

(式3-15)

となります※4。結果、VOFFSETを基準電圧(コモンモード電圧)として、VC1が-、VC2が+の電圧を出力することとなり、VEの値は異なりますがVC1とVC2は(2)と同じ結果になります。

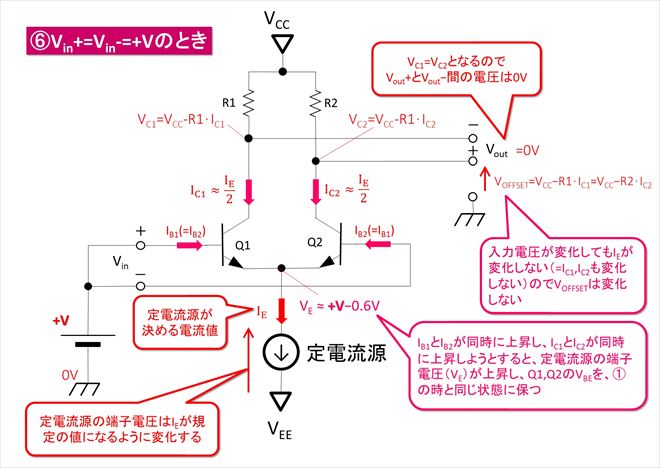

(6) Vin+=Vin-=+Vのとき

最後にVin+端子に+V[V]、Vin−端子に+V[V]の入力電圧が加わった時の回路各部の電圧・電流は図9のようになります。

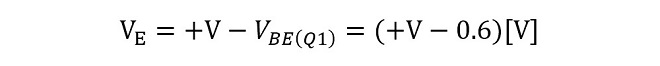

図9においては、Vin+、Vin−共に+V[V]、つまりコモンモード電圧+V[V]、ノーマルモード電圧は0Vの状態ですので、VE≈+V−0.6Vまで上昇しますが、IEは定電流回路の動作で(1)と同じになります。Q1とQ2は全く同じ特性なので

(式3-16)

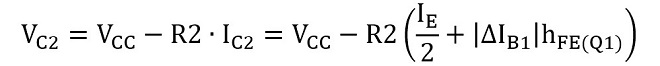

となります。この時の出力電圧は+電源VCCの値から、R1、R2の電圧降下分を弾いた値で、

(式3-17)

(式3-18)

となります。入力のコモンモード電圧の大きさには関係なく、出力のコモンモード電圧はVC1(=VC2)、ノーマルモード電圧(差動電圧)は0Vとなります。

4. 第9話のまとめ

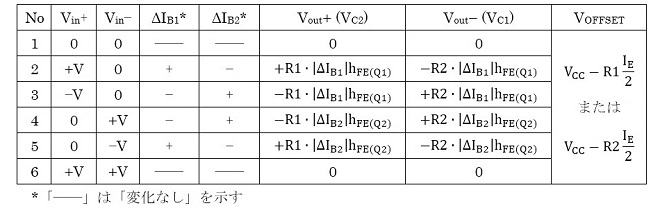

以上、ご説明した事を整理すると、差動増幅器(エミッタの回路を共通にした2つの増幅器ペア)の動作は表1のようになります。

表1 差動増幅回路の入出力電圧の関係※4

本表から以下の事がお解り頂けると思います。

①差動増幅回路の出力はVin+、Vin−の差電圧(Vin+−Vin_)のみで決まり、Vin+、Vin−の絶対値には影響されない。

②片方の入力が0V(GNDに接続)になっていたとしても、VOUT+、VOUT-は両方が対称に変化する。

③Vin+、Vin−に同じ値の電圧が印加されても、出力のオフセット電圧VOFFSETは変化しない。

これら通常の増幅器と異なる特徴的な動作は、Q1、Q2のエミッタを接続して共通回路にすることで実現しています。なお、ここまでの解説は全てQ1とQ2が「全く同じ」特性で動作することを前提としています。「全く同じ」とは特性が完全に一致しており、かつ温度・湿度などの動作環境条件が全く同じと見なせる状態を示します。この条件を満足するには同じ型名のトランジスタを持ってきただけでは不十分で、同一シリコンウェハ上で、かつその成分構成が完全に同一と見なせる極狭い領域に形成されたトランジスタを環境条件が同一と見なせる極狭い空間で使用する必要があります。この条件を満足しているのはモノリシックICのチップ上のみであり、基本的にICの内部回路で構成することにより威力を発揮する回路といえます。

今月は差動増幅の動作を説明するだけで力尽きてしまいました。次回は差動増幅を実現する為のもう一つの要素回路「カレントミラー回路」について解説し、その後、ギルバートセルに戻りたいと考えます。

※1: バリー・ギルバート博士については下記URLを参照

バリー・ギルバート Wikipedia

バリー・ギルバート(BARRIE GILBERT)、全米技術アカデミー会員に選出 | アナログ・デバイセズ (analog.com)

※2: (+A)×(+B)、 (+A)×(-B)、 (-A)×(+B)、 (-A)×(-B)の全ての組み合わせの乗算を示す。

※3: コモンモード/ノーマルモードについては、「Mr. Smithとインピーダンスマッチングの話【第39話】 アンテナと空間のインピーダンス(その6 平衡と不平衡(その2))」で解説しています。

※4: 本稿ではIC1、IC2に関する各計算式において、「ΔIB1」、「ΔIB2」を図4の状態におけるIB1、IB2との差分を示す記号として使用しています。また図5~図8中でIC1、IC2を導出する計算式はΔIB〇を使用していますが、本文中の計算式(式3-5、3-6、3-8、3-9、3-10、3-12、3-14、3-15、ならびに表1の計算式)では電流の増減(=VCの減増)を判りやすくする為に、ΔIB〇(〇は1、または2)の絶対値|ΔIB〇|を用いています。ΔIB〇で表現した式ではIC〇の増減分を示す項の極性符号は代入したIB〇が相手のトランジスタの値の場合に(-)で自身の値の場合は(+)、|ΔIB〇|で表現した式ではIB〇が図4の状態におけるIB〇より増える場合に(+)、減る場合に(-)になります。

今更聞けない無線と回路設計の話 バックナンバー

- 【テーマ2】デシベルと無線工学 (第19話) レベルダイヤグラムの縦軸(その3)

- 【テーマ2】デシベルと無線工学 (第18話) レベルダイヤグラムの縦軸(その2)

- 【テーマ2】デシベルと無線工学 (第17話) レベルダイヤグラムの縦軸(その1)

- 【テーマ2】デシベルと無線工学 (第16話) レベルダイヤグラムの構成

- 【テーマ2】デシベルと無線工学 (第15話) 非線形歪み(その5)

- 【テーマ2】デシベルと無線工学 (第14話) 非線形歪み(その4)

- 【テーマ2】デシベルと無線工学 (第13話) 非線形歪み(その3)

- 【テーマ2】デシベルと無線工学 (第12話) 非線形歪み(その2)

- 【テーマ2】デシベルと無線工学 (第11話) 非線形歪み(その1)

- 【テーマ2】デシベルと無線工学 (第10話) 線形歪み(フェージング現象)

- 【テーマ2】デシベルと無線工学 (第9話) 足される雑音と掛けられる雑音

- 【テーマ2】デシベルと無線工学 (第8話) 等価雑音の内訳

- 【テーマ2】デシベルと無線工学 (第7話) 無線通信の成立条件(その3)

- 【テーマ2】デシベルと無線工学 (第6話) 無線通信の成立条件(その2)

- 【テーマ2】デシベルと無線工学 (第5話) 無線通信の成立条件

- 【テーマ2】デシベルと無線工学 (第4話) dBmとdBµVの複雑な関係

- 【テーマ2】デシベルと無線工学 (第3話) dB(デシベル)を知る(その2)

- 【テーマ2】デシベルと無線工学 (第2話) dB(デシベル)を知る(その1)

- 【テーマ2】デシベルと無線工学 (第1話) (プロローグ)無線通信機の天井と床

- 【テーマ1】三角関数のかけ算と無線工学 (第30話) 三角関数のかけ算と無線工学の切っても切れない深い縁

- 【テーマ1】三角関数のかけ算と無線工学 (第29話) 交流ベクトル空間と直交ミキサ(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第28話) 交流ベクトル空間と直交ミキサ(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第27話) 交流ベクトル空間と直交ミキサ(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第26話) 交流ベクトル空間と直交ミキサ

- 【テーマ1】三角関数のかけ算と無線工学 (第25話) マイナスの周波数

- 【テーマ1】三角関数のかけ算と無線工学 (第24話) 同一周波数のサイン波の掛け算と周波数の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第23話) 同一周波数のサイン波の掛け算と周波数の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第22話) 同一周波数のサイン波の掛け算と周波数の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第21話) ループフィルタとPLLの応答特性の話(その6)

- 【テーマ1】三角関数のかけ算と無線工学 (第20話) ループフィルタとPLLの応答特性の話(その5)

- 【テーマ1】三角関数のかけ算と無線工学 (第19話) ループフィルタとPLLの応答特性の話(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第18話) ループフィルタとPLLの応答特性の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第17話) ループフィルタとPLLの応答特性の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第16話) ループフィルタとPLLの応答特性の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第15話) 位相検波器の話

- 【テーマ1】三角関数のかけ算と無線工学 (第14話) PLLの動作原理と代表構成

- 【テーマ1】三角関数のかけ算と無線工学 (第13話) PLLの役割とサイン波の純度について

- 【テーマ1】三角関数のかけ算と無線工学 (第12話) 同一周波数のサイン波のかけ算と位相のはなし

- 【テーマ1】三角関数のかけ算と無線工学 (第11話) ギルバートセル乗算器(その3・ギルバートセル乗算回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第10話) ギルバートセル乗算器(その2・定電流源とカレントミラー回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第9話) ギルバートセル乗算器(その1・差動増幅の基礎)

- 【テーマ1】三角関数のかけ算と無線工学 (第8話) ダブルバランスドミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第7話) ダブルバランスドミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第6話) トランジスタミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第5話) トランジスタミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第4話) 非線形動作を利用したかけ算のまとめ

- 【テーマ1】三角関数のかけ算と無線工学 (第3話) ミキサの線形性って何?

- 【テーマ1】三角関数のかけ算と無線工学 (第2話) 周波数変換とミキサ(混合)回路

- 【テーマ1】三角関数のかけ算と無線工学 (第1話) サイン波のかけ算

お知らせ

-

2022.11.15

11月号後半の記事をアップしました

-

2022.11.1

11月号の記事をアップしました

-

2022.10.17

10月号後半の記事をアップしました

-

2022.10.3

10月号の記事をアップしました

-

2022.9.15

9月号後半の記事をアップしました

-

2022.9.1

9月号の記事をアップしました

-

2022.8.15

8月号後半の記事をアップしました

-

2022.8.1

8月号の記事をアップしました

-

2022.7.15

7月号後半の記事をアップしました

-

2022.7.1

7月号の記事をアップしました

-

2022.6.15

6月号後半の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JL3ZGL」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2022.6.1

6月号の記事をアップしました

6月4日(土)、JH1CBX/3が14MHz SSBに初オンエアします。 入感がありましたらぜひお声がけください。 -

2022.5.16

5月号後半の記事をアップしました

-

2022.5.2

5月号の記事をアップしました

5月14日(土)、JL3ZGLはオペレーターにMasacoさんを迎えHAMtte交信パーティに 参加します。詳しくは4月号のニュースをご確認ください。 -

2022.4.15

4月号後半の記事をアップしました

-

2022.4.1

4月号の記事をアップしました

-

2022.3.15

3月号後半の記事をアップしました

-

2022.3.1

3月号の記事をアップしました

-

2022.2.15

2月号後半の記事をアップしました

-

2022.2.1

2月号の記事をアップしました

-

2022.1.17

1月号後半の記事をアップしました

-

2022.1.5

1月号の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JA3YUA」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2021.12.15

12月号後半の記事をアップしました

-

2021.12.1

12月号の記事をアップしました

-

2021.11.15

11月号後半の記事をアップしました

-

2021.11.01

2021年11月号の記事をアップしました

-

2021.10.15

10月号後半の記事をアップしました

-

2021.10.01

2021年10月号の記事をアップしました

-

2021.09.15

9月号後半の記事をアップしました

-

2021.09.01

2021年9月号の記事をアップしました

-

2021.08.16

8月号後半の記事をアップしました

-

2021.08.02

2021年8月号の記事をアップしました

-

2021.07.15

7月号後半の記事をアップしました

-

2021.07.01

2021年7月号の記事をアップしました

-

2021.06.15

6月号後半の記事をアップしました

-

2021.06.01

2021年6月号の記事をアップしました

-

2021.05.17

5月号後半の記事をアップしました

-

2021.05.06

2021年5月号の記事をアップしました

-

2021.04.15

4月号後半の記事をアップしました

-

2021.04.01

2021年4月号の記事をアップしました

連載記事 Masacoの「むせんのせかい」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.15

3月号後半の記事をアップしました

連載記事「今月のハム」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.01

2021年3月号の記事をアップしました

-

2021.02.15

2月号後半の記事をアップしました

-

2021.02.01

2021年2月号の記事をアップしました

-

2021.01.15

1月号後半の記事をアップしました

-

2021.01.05

2021年1月号の記事をアップしました

-

2020.12.15

12月号後半の記事をアップしました

-

2020.12.01

2020年12月号の記事をアップしました

-

2020.11.16

11月号後半の記事をアップしました

-

2020.11.02

2020年11月号の記事をアップしました

-

2020.10.15

10月号後半の記事をアップしました

-

2020.10.01

2020年10月号の記事をアップしました

-

2020.09.15

9月号後半の記事をアップしました

-

2020.09.01

2020年9月号の記事をアップしました

-

2020.08.17

8月号後半の記事をアップしました

-

2020.08.03

2020年8月号の記事をアップしました

-

2020.07.15

7月号後半の記事をアップしました

-

2020.07.01

2020年7月号の記事をアップしました

-

2020.06.15

6月号後半の記事をアップしました

-

2020.06.01

2020年6月号の記事をアップしました

-

2020.05.01

2020年5月号の記事をアップしました

-

2020.04.15

4月号後半の記事をアップしました

-

2020.04.01

2020年4月号の記事をアップしました

-

2020.03.16

3月号後半の記事をアップしました

-

2020.03.09

JARD、eラーニングでのアマチュア無線国家資格取得を呼び掛けるお知らせを、臨時休校で自宅待機中の小中高生に向けて発表。詳しくはこちら。

-

2020.03.02

2020年3月号の記事をアップしました

-

2020.02.17

2月号後半の記事をアップしました

-

2020.02.03

2020年2月号の記事をアップしました

-

2020.01.15

1月号後半の記事をアップしました

-

2020.01.06

2020年1月号の記事をアップしました

-

2019.12.16

12月号後半の記事をアップしました

-

2019.12.02

2019年12月号の記事をアップしました

-

2019.11.15

11月号後半の記事をアップしました

-

2019.11.01

2019年11月号の記事をアップしました

-

2019.10.15

10月号後半の記事をアップしました

-

2019.10.01

2019年10月号の記事をアップしました

-

2019.09.17

9月号後半の記事をアップしました

-

2019.09.02

2019年9月号の記事をアップしました

-

2019.08.16

8月号後半の記事をアップしました

-

2019.08.01

2019年8月号の記事をアップしました

-

2019.07.16

7月号後半の記事をアップしました

-

2019.07.01

2019年7月号の記事をアップしました

-

2019.06.17

6月号後半の記事をアップしました

-

2019.06.01

2019年6月号の記事をアップしました

-

2019.05.20

5月号後半の記事をアップしました

-

2019.05.07

2019年5月号の記事をアップしました

-

2019.04.15

4月号後半の記事をアップしました

-

2019.04.01

2019年4月号の記事をアップしました

-

2019.03.15

3月号後半の記事をアップしました

-

2019.03.01

2019年3月号の記事をアップしました

-

2019.02.15

2月号後半の記事をアップしました

-

2019.02.01

2019年2月号の記事をアップしました

-

2019.01.18

1月号後半の記事をアップしました

-

2019.01.07

2019年1月号の記事をアップしました

-

2018.12.17

12月号後半の記事をアップしました

-

2018.12.01

2018年12月号の記事をアップしました

-

2018.11.15

11月号後半の記事をアップしました

-

2018.11.01

2018年11月号の記事をアップしました

-

2018.10.15

10月号後半の記事をアップしました

-

2018.10.01

2018年10月号の記事をアップしました

-

2018.09.15

9月号後半の記事をアップしました

-

2018.09.01

2018年9月号の記事をアップしました

-

2018.08.17

8月号後半の記事をアップしました

-

2018.08.01

2018年8月号の記事をアップしました

-

2018.07.17

7月号後半の記事をアップしました

-

2018.07.02

2018年7月号の記事をアップしました

-

2018.06.15

6月号後半の記事をアップしました

-

2018.06.01

2018年6月号の記事をアップしました

-

2018.05.15

5月号後半の記事をアップしました

-

2018.05.01

2018年5月号の記事をアップしました

-

2018.04.16

4月号後半の記事をアップしました

-

2018.04.02

2018年4月号の記事をアップしました

-

2018.03.15

3月号後半の記事をアップしました

-

2018.03.01

2018年3月号の記事をアップしました

-

2018.02.15

2月号後半の記事をアップしました

-

2018.02.01

2018年2月号の記事をアップしました

-

2018.01.15

1月号後半の記事をアップしました

-

2018.01.05

2018年1月号の記事をアップしました

-

2017.12.15

12月号後半の記事をアップしました

-

2017.12.1

12月号をアップしました

-

2017.11.15

11月号後半の記事をアップしました

-

2017.11.1

11月号をアップしました

-

2017.10.16

10月号後半の記事をアップしました

-

2017.10.2

10月号をアップしました

-

2017.9.15

What a healthy time! ~健康を応援する特別なお料理~/第3回 食物繊維たっぷり! 海藻の和風リゾット、FB Monthly Fashion/第9回 秋っぽい柄&色コーデ、子供の無線教室/第9回 「アンテナの形や大きさに注目!!」を掲載しました

-

2017.9.4

<速報>ハムフェア2017を掲載しました

-

2017.9.1

9月号をアップしました

-

2017.8.17

What a healthy time! ~健康を応援する特別なお料理~/第2回 和風のポトフ 納豆ソース添え、FB Monthly Fashion/第8回 夏のお出かけコーデ、子供の無線教室/第8回 「無線機にはどんなものがあるの?」を掲載しました

-

2017.8.1

8月号をアップしました

-

2017.7.18

What a healthy time! ~健康を応援する特別なお料理~/第1回 メロンの冷製スープ ナッツのアイスクリームのせ、FB Monthly Fashion/第7回 コットンTシャツコーデとボーイズコーデ、子供の無線教室/第7回 「電波はどうやって海外や宇宙に届くの?」を掲載しました

-

2017.7.1

7月号をアップしました

-

2017.6.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第9回 FB Girlsの野望 with ムースと甘エビのタルタル、FB Monthly Fashion/第6回 雨の日コーデと親子コーデ、子供の無線教室/第6回 「電波はいろいろなところで大活躍!!」を掲載しました

-

2017.6.1

6月号をアップしました

-

2017.5.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第8回 番外編 春うらら♪豪華弁当でお花見、FB Monthly Fashion/第5回 ブラウス&シャツを使ったコーディネート、子供の無線教室/第5回 「周波数によって変わる、電波の特徴」を掲載しました

-

2017.5.1

5月号をアップしました

-

2017.4.17

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第7回 ARDFの思い出 with 2種類のソースのカルボナーラ、FB Monthly Fashion/第4回 Gジャンを使ったコーディネート、子供の無線教室/第4回 「電波の性質を覚えよう」を掲載しました

-

2017.4.1

4月号をアップしました

-

2017.3.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第6回 初めてのQSOの思い出 with グリーンのアクアパッツァ、FB Monthly Fashion/第3回 ピンクを使ったコーディネート、子供の無線教室/第3回 「電波はどうやって伝わるの?」を掲載しました

-

2017.3.1

3月号をアップしました

-

2017.2.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第5回 FB Girlsの試験の思い出 withウマ辛和風スープ、FB Monthly Fashion/第2回 デニムと明るめニットのコーディネートを掲載しました

-

2017.2.1

2月号をアップしました

-

2017.1.16

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第4回 YLハムを増やす秘策とは?! withおなかにやさしいお料理、【新連載】FB Monthly Fashion/第1回 アウター別おすすめコーディネート(ライダース・ノーカラー・ダッフル)を掲載しました

-

2017.1.5

1月号をアップしました

-

2016.12.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第3回 YLハムの行く年来る年 with ブイヤベースの洋風お鍋を掲載しました

-

2016.12.1

12月号をアップしました

-

2016.11.15

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(後編)!、What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第2回 YLハムの悩み解決!with サケのフレンチトーストを掲載しました

-

2016.11.1

11月号をアップしました

-

2016.10.17

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(前編)!、【新連載】What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第1回 FB GirlsのプライベートQSO with 土瓶蒸しのリゾットを掲載しました

外部リンク

アマチュア無線関連機関/団体

各総合通信局/総合通信事務所

アマチュア無線機器メーカー(JAIA会員)

次号は 12月 1日(木) に公開予定