FBのトレビア

第二十四回 今さらPLLの原理について

Dr. FB

ちょっとした電子工作や無線機の調整にはSG(Signal Generator)が役に立ちます。市販のSGなら出力レベルも正確ですが、自作派のSGならアッテネーターの製作もありますのでそう簡単にいきません。無線機のテストにSGが欲しいと思いその製作を考えているうちにPLL(Phase Locked Loop)の原理に行きつきました。今回は1アマの試験でもたいへんよく出題されているPLLの原理について簡単に説明します。

まずは1アマの過去問出題から

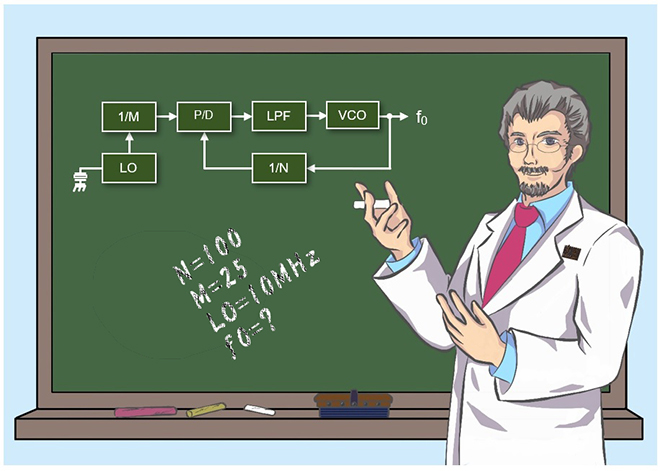

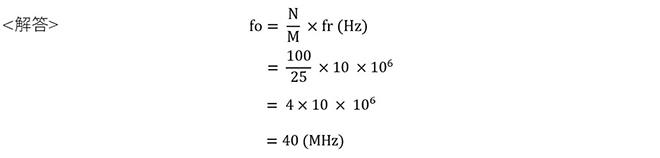

図1に掲載した問題は、第1級アマチュア無線技士の工学に出題された問題です。これに類似するPLLの問題は、平成16年から令和3年までの18年間になんと13回も出題されています。結構出題頻度の高い問題です。

図1 第1級アマチュア無線技士工学の問題(平成29年4月実施 日本無線協会)

PLL導入の時代背景

PLLの原理を説明する前に、(1)水晶振動子を使ったトランシーバーを簡単に説明してから(2)PLLの概要を説明します。そして、それ以降は各々のブロックの説明を行います。

(1) 水晶振動子を使ったトランシーバー

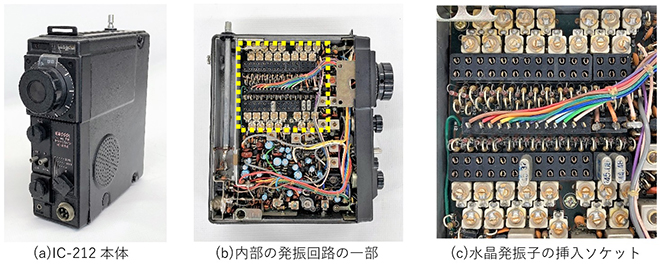

図2を参照してください。図2は、1976年に発売されたアイコムのIC-212、144MHz 15チャンネルFMポータブルトランシーバーです。

図2 IC-212 15チャンネルFMポータブルトランシーバー

ケースを開けると図2(b)に15チャンネル分の水晶振動子(クリスタルともいいます)を挿入するソケットが点線の部分に見ることができます。図2(c)はその拡大図です。15チャンネル分の水晶振動子はそれぞれ送信、受信分が必要となり、フルチャンネルを装備しようとすると30個もの水晶振動子が必要になります。

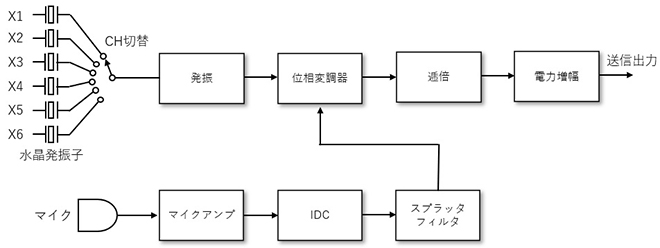

図3 6チャンネルFMトランシーバーの送信部のブロックダイヤグラム

図3のX1~X6は水晶振動子です。今でこそ、トランシーバーを購入するとどの周波数でもダイヤルを回すと送受信できます。上記のIC-212が発売された頃は、希望の周波数で送受信しようとすると希望の周波数の水晶振動子を無線機に挿入しなければなりませんでした。例えば2メーターバンドであれば、145.00MHz~145.98MHzまでのFM 20kHzピッチのチャンネルは50チャンネルあります。好きなチャンネルでQSOをしようと思えば100個の水晶を予め準備しておく必要があります。水晶振動子も物理的な大きさが存在しますので、100個もの水晶振動子を無線機に全部挿入しようとすると、これも物理的なスペースが必要になります。そうなると無線機もたいへん大きなものとなってしまいます。必然と大きさを選ぶか、チャンネル数を選ぶかといった問題にあたります。

(2) VFOではダメか

水晶振動子を使わなくてもL(コイル)とC(コンデンサ)でVFO(Variable Frequency Oscillator)と呼ばれる発振回路を作ることができます。VFOは日本語では、可変周波数発振器と呼んでいます。VFOは水晶振動子の代わりとなり、連続した周波数の信号を作り出すことができますので、その信号を局部発振回路の信号として使うとどの周波数でも送受信できることになります。

ところが回路はLとCで構成された発振回路ですので外部の振動や周囲の温度、湿度に大きく影響を受けることになり、通信機の安定度の観点からすればなかなか難しいところがあります。水晶振動子でも同様に外部要因による周波数の変動を生じますが、VFOの周波数変動と比較すると周波数安定度は抜群です。

PLLの理論は20世紀の初めにはすでに発電機の周波数制御に使われていたと書物に記載されていました。通信機の分野でPLLが使われだしたのは1920年代にラジオ放送が始まってからとのことです。民生用機器に導入しようとすると当時の部品からして膨大なコストとスペースが必要だったのだと思います。

PLLもVFOのように特殊な部品が使われている訳ではありません。特殊と言えば、周波数の安定度を制御する方法だけです。VFOは温度変化に対して、温度の変化を打ち消すような部品を使って温度補償を行い、周波数を安定させていました。PLLでは水晶振動子の安定度に合わせるように常に電気的に自動制御が行われるような回路で周波数を安定させています。

PLLの概要

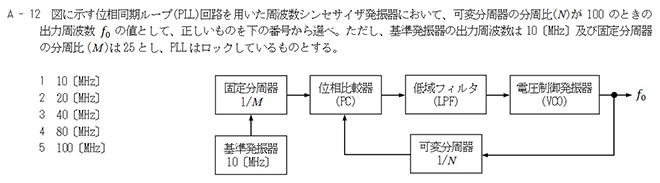

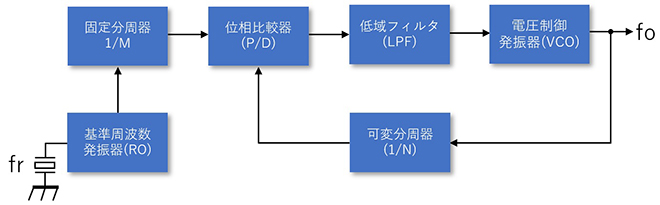

(1) PLL回路のブロックダイヤグラム

PLLは一種の帰還回路です。図4に示したようにPLLの基本回路は、基準周波数発振器(Reference Oscillator)、固定分周器(Fixed Divider)、位相比較器(Phase Detector)、低域フィルタ(Low Pass Filter/LPF)、VCO(Voltage Controlled Oscillator)、それに可変分周器(Programmable Divider)の各回路で構成されています。

LCで発振させた信号をそのまま無線機の局部発振回路の信号に注入することもできますが、周波数の安定度は非常に悪く、安定した通信を行うことができません。

図4 通信機に使われるPLLの原理図

そこで図4に示したPLLが登場するわけで、基準周波数発振器で発振させた信号frとVCOで発振させた信号foの2信号を位相比較器で比較し、それら2信号の位相差に応じた出力電圧を用いてVCOの発振周波数を制御し、安定させます。例えば、発振周波数が高ければ位相比較器の出力電圧を下げる、あるいはその逆のように制御します。その制御の方法は後述するVCOでもう少し詳しく説明します。

(2) 固定分周器(1/M)

これは、入力された周波数を整数分の1にする回路です。たいていは分周専用のICを用います。冒頭に示した1アマの問題ではM=25となっています。つまり、入力された10MHzの信号を25分の1、つまり400kHzにして出力する回路です。

(3) 可変分周器(1/N)

プログラマブル・ディバイダ―とも呼ばれます。任意の分周比を外部端子で設定することができます。CPUと組み合わせることで、無線機のダイヤルを回すと分周比が変化し、可変分周器(1/N)から出力される信号の周波数を変えることができます。

(4) 位相比較器(Phase Detector)

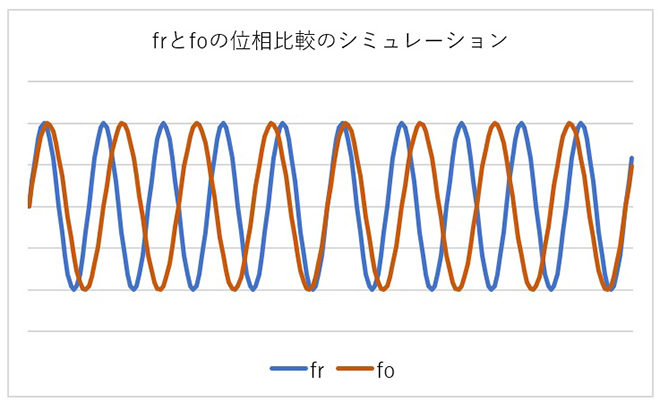

位相の比較とは、別の言い方をすれば周波数の比較をするという意味です。位相比較器に入力される1つの信号fr/Mは、元は水晶振動子の発振ですから抜群の安定度を持っています。その周波数にもう一つのVCOの信号fo/Nがぴったり合致すれば図5の二つの正弦波は重なり、位相差がなくなります。つまり、2つの周波数は合致したことになります。

図5 frとfoの位相比較

位相比較器にはいろいろな方式があるようですが、例えば、古い方式ですとfrとfoの信号のビート(うなり)の周波数を取り、そのビート周波数に沿った電圧を出力する位相比較器もあるようです。つまりf-V変換です。ビート周波数が0のときは位相比較器の出力電圧は0(V)。ビートが発生するとそれに応じた電圧を出力するといった具合です。

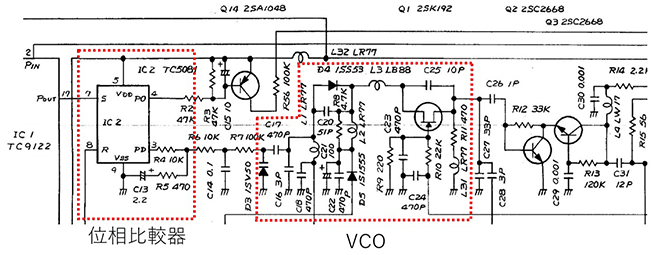

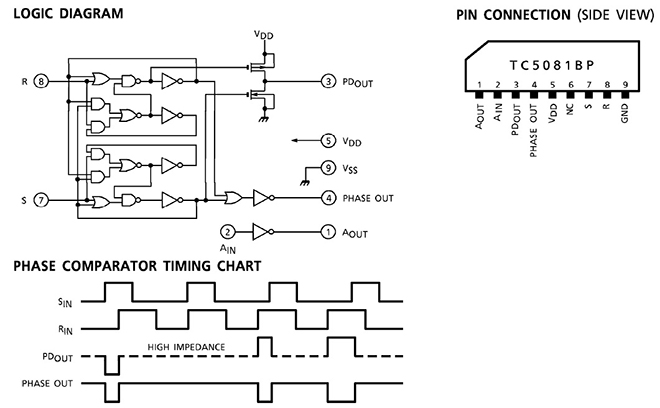

図6は、アイコムのIC-2N(1980年発売)に使われていたPLLの回路の一部です。IC2(TC5081)がその位相比較器のICです。すでにこのICは製造中止となり流通在庫しか残ってないようですが、自作派には使いやすいICです。

図6 IC-2Nの位相比較器とVCO周辺の回路(アイコムIC-2Nの回路図より抜粋)

図7 IC-2Nに使われていた位相比較器ICの内部回路とそのタイミングチャート(TOSHIBA TC5081のデータシートより引用)

(5) 低域フィルタ(Low Pass Filter)

ループフィルタ(Loop Filter)とも呼ばれます。図6の回路図ではR4、R5、R6、C13、C14で構成されています。位相比較器の出力には雑音や高周波成分が含まれていますからそれらを取り除きVCOのD3に供給するDC成分の信号を作ります。

(6) 電圧制御発振器(VCO)

図6のQ1(2SK192)とその周辺回路で構成された回路がVCO(Voltage Controlled Oscillator)の回路です。コルピッツ発振回路でキーパーツがD3(1SV50)のバラクターダイオードです。

VCOは、LとCで構成された発振回路であると述べましたが、その部品の一部にバラクターダイオードが使われているところがミソです。バラクターダイオードとは、ダイオードの一種ですが、逆方向に電圧を印加することでアノード、カソード間の静電容量が変化するという特性の持ったダイオードです。つまり、このバラクターダイオードのC(静電容量)をLCの発振回路に用い、このCの静電容量の変化でVCOの発振周波数を可変しています。

位相比較器で比較したfrとfoに位相差が発生するとき、その位相差が大きい時には位相比較器から出力される電圧が大きく、逆のときは低い電圧となります。その電圧をVCO内のバラクターダイオードに加えることで、VCOの発振周波数を可変させ基準周波数frと同じ周波数になるようにするのがPLLです。

frとfoの関係

基準周波数発振器(RO)で発振した信号を固定分周器(1/M)で分周した周波数をf1とします。また、VCOの出力信号(fo)を可変分周器(1/N)で分周した周波数をf2とします。PLLは、f1とf2の間の関係をf1=f2とする一種の帰還を掛けた自動制御の回路です。f1=f2となったとき、我々は「PLLはロック(Lock)した」と言います。反対に何らかの原因でf1=f2となっていない場合、「PLLはアンロック(Unlock)の状態」であるといいます。

基準周波数発振器(RO)の周波数は、図8ではfrです。frの周波数は、MHzオーダーの高い周波数ですから、それを低い周波数にするために分周器(1/M)で分周します。その分周した固定分周器の出力周波数f1は、f1=fr/Mとなります。VCOの発振周波数を予め希望目的周波数としてLC回路で設計しておきます。希望目的周波数foは、無線機の回路の局部発振回路(LO)等に使われる信号ですので、無線機のダイヤルを回すと周波数が変わります。そのため可変分周器(1/N)を外部からプログラムで絶えずf1の周波数となるように分周比を決めます。つまり、f2は、VCOの出力周波数(fo)をN分の1した周波数ですので、f2=fo/Nとなります。

図8 frとfoの関係

先にも説明しましたように、f1=f2がPLLのロック状態の条件ですからf1とf2の関係式からVCOの出力周波数を求めると下のようになります。

IC-2NのPLL回路

IC-2NのPLL回路では、fr=5.12MHzの水晶振動子が使われています。その5.12MHzを固定分周器(1/M)で1024分周しており、5kHzの信号をf1として位相比較器に入力しています。位相比較器に入るもう一つの信号f2は、VCOの出力周波数を分周して5kHzを得ています。ここで、M、frは一定ですので分周比Nを可変することでVCOの出力周波数(fo)が変わることが理解できます。

FBDX

<参考とした資料>

公益財団法人日本無線協会 平成29年4月実施の無線工学過去問

産報出版株式会社 電子科学シリーズ PLL-ICの使い方

誠文堂新光社 わかる半導体シリーズ PLL活用ガイド

TOSHIBA TC5081データシート

アイコム(株) IC-2N回路図

FBのトレビア バックナンバー

- 第四十六回 JARLライフメンバーバッジが届いた!

- 第四十五回 カウンターICとラダー抵抗によるD/A変換回路でのこぎり波を作る実験

- 第四十四回 ラダー抵抗によるD/A変換について

- 第四十三回 電子ホタルの製作とその解析

- 第四十二回 DCモータの回転数制御について

- 第四十一回 74HC192と74HC4511を使ったアップダウンカウンタの説明

- 第四十回 単電源から正負両電源を作る

- 第三十九回 ホワイトノイズジェネレータでフィルタの特性を見る?

- 第三十八回 ツイストペアケーブルのノイズ軽減は本当か?

- 第三十七回 74HC74を使った分周回路の実験

- 第三十六回 電圧可変抵抗器の考察

- 第三十五回 tinySAで見るひずみ波形のスペクトラム

- 第三十四回 FM放送受信用のQFHアンテナを作ってみた

- 第三十三回 コイルのインダクタンスについて

- 第三十二回 アナログスイッチの動作について

- 第三十一回 小型デジタル電圧計、2線式と3線式は何が違う?

- 第三十回 Back to Backアンテナ、その後の検証

- 第二十九回 オペアンプを使った定電流回路について

- 第二十八回 UHFに対する同軸ケーブルのロス

- 第二十七回 2.4GHz無線LANアンテナ

- 第二十六回 MOSFETを使ってみよう

- 第二十五回 コンパレータについて

- 第二十四回 今さらPLLの原理について

- 第二十三回 MLAの性能をチェック

- 第二十二回 SHF帯のフレネルゾーンについて

- 第二十一回 SGの解放端と負荷端のレベルの差

- 第二十回 Made in Japanは健在か(再び変換コネクター)

- 第十九回 Back to Backアンテナの実用の可能性

- 第十八回 SWR測定、アンテナ直下がベストは本当だった

- 第十七回 受信感度低下の正体はBNC L型コネクターか

- 第十六回 サイン、コサインは役に立つ

- 第十五回 BIRD 43はほんとうに正確か

- 第十四回 ダイポールアンテナにバランは必要か

- 第十三回 ゲルマニウムラジオは何故シリコンラジオと呼ばれないか?

- 第十二回 7セグメントLEDの点灯

- 第十一回 ハンディー機のアンテナSWRと送受信の相関を検証 (その3)

- 第十回 ハンディー機のアンテナSWRの測定(その2)

- 第九回 ハンディー機のアンテナSWRの測定(その1)

- 第八回 CM形電力計

- 第七回 V/UHF帯3バンドアンテナ解体新書

- 第六回 トリプレクサーってなんだ

- 第五回 アナログメーターのちょっと変わったスペック

- 第四回 50Ω不平衡ってなんのこと

- 第三回 マルチバンドアンテナのトラップのお話

- 第二回 dBm(デービーエム)のお話

- 第一回 dB(デシベル)のお話

お知らせ

-

2022.11.15

11月号後半の記事をアップしました

-

2022.11.1

11月号の記事をアップしました

-

2022.10.17

10月号後半の記事をアップしました

-

2022.10.3

10月号の記事をアップしました

-

2022.9.15

9月号後半の記事をアップしました

-

2022.9.1

9月号の記事をアップしました

-

2022.8.15

8月号後半の記事をアップしました

-

2022.8.1

8月号の記事をアップしました

-

2022.7.15

7月号後半の記事をアップしました

-

2022.7.1

7月号の記事をアップしました

-

2022.6.15

6月号後半の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JL3ZGL」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2022.6.1

6月号の記事をアップしました

6月4日(土)、JH1CBX/3が14MHz SSBに初オンエアします。 入感がありましたらぜひお声がけください。 -

2022.5.16

5月号後半の記事をアップしました

-

2022.5.2

5月号の記事をアップしました

5月14日(土)、JL3ZGLはオペレーターにMasacoさんを迎えHAMtte交信パーティに 参加します。詳しくは4月号のニュースをご確認ください。 -

2022.4.15

4月号後半の記事をアップしました

-

2022.4.1

4月号の記事をアップしました

-

2022.3.15

3月号後半の記事をアップしました

-

2022.3.1

3月号の記事をアップしました

-

2022.2.15

2月号後半の記事をアップしました

-

2022.2.1

2月号の記事をアップしました

-

2022.1.17

1月号後半の記事をアップしました

-

2022.1.5

1月号の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JA3YUA」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2021.12.15

12月号後半の記事をアップしました

-

2021.12.1

12月号の記事をアップしました

-

2021.11.15

11月号後半の記事をアップしました

-

2021.11.01

2021年11月号の記事をアップしました

-

2021.10.15

10月号後半の記事をアップしました

-

2021.10.01

2021年10月号の記事をアップしました

-

2021.09.15

9月号後半の記事をアップしました

-

2021.09.01

2021年9月号の記事をアップしました

-

2021.08.16

8月号後半の記事をアップしました

-

2021.08.02

2021年8月号の記事をアップしました

-

2021.07.15

7月号後半の記事をアップしました

-

2021.07.01

2021年7月号の記事をアップしました

-

2021.06.15

6月号後半の記事をアップしました

-

2021.06.01

2021年6月号の記事をアップしました

-

2021.05.17

5月号後半の記事をアップしました

-

2021.05.06

2021年5月号の記事をアップしました

-

2021.04.15

4月号後半の記事をアップしました

-

2021.04.01

2021年4月号の記事をアップしました

連載記事 Masacoの「むせんのせかい」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.15

3月号後半の記事をアップしました

連載記事「今月のハム」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.01

2021年3月号の記事をアップしました

-

2021.02.15

2月号後半の記事をアップしました

-

2021.02.01

2021年2月号の記事をアップしました

-

2021.01.15

1月号後半の記事をアップしました

-

2021.01.05

2021年1月号の記事をアップしました

-

2020.12.15

12月号後半の記事をアップしました

-

2020.12.01

2020年12月号の記事をアップしました

-

2020.11.16

11月号後半の記事をアップしました

-

2020.11.02

2020年11月号の記事をアップしました

-

2020.10.15

10月号後半の記事をアップしました

-

2020.10.01

2020年10月号の記事をアップしました

-

2020.09.15

9月号後半の記事をアップしました

-

2020.09.01

2020年9月号の記事をアップしました

-

2020.08.17

8月号後半の記事をアップしました

-

2020.08.03

2020年8月号の記事をアップしました

-

2020.07.15

7月号後半の記事をアップしました

-

2020.07.01

2020年7月号の記事をアップしました

-

2020.06.15

6月号後半の記事をアップしました

-

2020.06.01

2020年6月号の記事をアップしました

-

2020.05.01

2020年5月号の記事をアップしました

-

2020.04.15

4月号後半の記事をアップしました

-

2020.04.01

2020年4月号の記事をアップしました

-

2020.03.16

3月号後半の記事をアップしました

-

2020.03.09

JARD、eラーニングでのアマチュア無線国家資格取得を呼び掛けるお知らせを、臨時休校で自宅待機中の小中高生に向けて発表。詳しくはこちら。

-

2020.03.02

2020年3月号の記事をアップしました

-

2020.02.17

2月号後半の記事をアップしました

-

2020.02.03

2020年2月号の記事をアップしました

-

2020.01.15

1月号後半の記事をアップしました

-

2020.01.06

2020年1月号の記事をアップしました

-

2019.12.16

12月号後半の記事をアップしました

-

2019.12.02

2019年12月号の記事をアップしました

-

2019.11.15

11月号後半の記事をアップしました

-

2019.11.01

2019年11月号の記事をアップしました

-

2019.10.15

10月号後半の記事をアップしました

-

2019.10.01

2019年10月号の記事をアップしました

-

2019.09.17

9月号後半の記事をアップしました

-

2019.09.02

2019年9月号の記事をアップしました

-

2019.08.16

8月号後半の記事をアップしました

-

2019.08.01

2019年8月号の記事をアップしました

-

2019.07.16

7月号後半の記事をアップしました

-

2019.07.01

2019年7月号の記事をアップしました

-

2019.06.17

6月号後半の記事をアップしました

-

2019.06.01

2019年6月号の記事をアップしました

-

2019.05.20

5月号後半の記事をアップしました

-

2019.05.07

2019年5月号の記事をアップしました

-

2019.04.15

4月号後半の記事をアップしました

-

2019.04.01

2019年4月号の記事をアップしました

-

2019.03.15

3月号後半の記事をアップしました

-

2019.03.01

2019年3月号の記事をアップしました

-

2019.02.15

2月号後半の記事をアップしました

-

2019.02.01

2019年2月号の記事をアップしました

-

2019.01.18

1月号後半の記事をアップしました

-

2019.01.07

2019年1月号の記事をアップしました

-

2018.12.17

12月号後半の記事をアップしました

-

2018.12.01

2018年12月号の記事をアップしました

-

2018.11.15

11月号後半の記事をアップしました

-

2018.11.01

2018年11月号の記事をアップしました

-

2018.10.15

10月号後半の記事をアップしました

-

2018.10.01

2018年10月号の記事をアップしました

-

2018.09.15

9月号後半の記事をアップしました

-

2018.09.01

2018年9月号の記事をアップしました

-

2018.08.17

8月号後半の記事をアップしました

-

2018.08.01

2018年8月号の記事をアップしました

-

2018.07.17

7月号後半の記事をアップしました

-

2018.07.02

2018年7月号の記事をアップしました

-

2018.06.15

6月号後半の記事をアップしました

-

2018.06.01

2018年6月号の記事をアップしました

-

2018.05.15

5月号後半の記事をアップしました

-

2018.05.01

2018年5月号の記事をアップしました

-

2018.04.16

4月号後半の記事をアップしました

-

2018.04.02

2018年4月号の記事をアップしました

-

2018.03.15

3月号後半の記事をアップしました

-

2018.03.01

2018年3月号の記事をアップしました

-

2018.02.15

2月号後半の記事をアップしました

-

2018.02.01

2018年2月号の記事をアップしました

-

2018.01.15

1月号後半の記事をアップしました

-

2018.01.05

2018年1月号の記事をアップしました

-

2017.12.15

12月号後半の記事をアップしました

-

2017.12.1

12月号をアップしました

-

2017.11.15

11月号後半の記事をアップしました

-

2017.11.1

11月号をアップしました

-

2017.10.16

10月号後半の記事をアップしました

-

2017.10.2

10月号をアップしました

-

2017.9.15

What a healthy time! ~健康を応援する特別なお料理~/第3回 食物繊維たっぷり! 海藻の和風リゾット、FB Monthly Fashion/第9回 秋っぽい柄&色コーデ、子供の無線教室/第9回 「アンテナの形や大きさに注目!!」を掲載しました

-

2017.9.4

<速報>ハムフェア2017を掲載しました

-

2017.9.1

9月号をアップしました

-

2017.8.17

What a healthy time! ~健康を応援する特別なお料理~/第2回 和風のポトフ 納豆ソース添え、FB Monthly Fashion/第8回 夏のお出かけコーデ、子供の無線教室/第8回 「無線機にはどんなものがあるの?」を掲載しました

-

2017.8.1

8月号をアップしました

-

2017.7.18

What a healthy time! ~健康を応援する特別なお料理~/第1回 メロンの冷製スープ ナッツのアイスクリームのせ、FB Monthly Fashion/第7回 コットンTシャツコーデとボーイズコーデ、子供の無線教室/第7回 「電波はどうやって海外や宇宙に届くの?」を掲載しました

-

2017.7.1

7月号をアップしました

-

2017.6.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第9回 FB Girlsの野望 with ムースと甘エビのタルタル、FB Monthly Fashion/第6回 雨の日コーデと親子コーデ、子供の無線教室/第6回 「電波はいろいろなところで大活躍!!」を掲載しました

-

2017.6.1

6月号をアップしました

-

2017.5.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第8回 番外編 春うらら♪豪華弁当でお花見、FB Monthly Fashion/第5回 ブラウス&シャツを使ったコーディネート、子供の無線教室/第5回 「周波数によって変わる、電波の特徴」を掲載しました

-

2017.5.1

5月号をアップしました

-

2017.4.17

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第7回 ARDFの思い出 with 2種類のソースのカルボナーラ、FB Monthly Fashion/第4回 Gジャンを使ったコーディネート、子供の無線教室/第4回 「電波の性質を覚えよう」を掲載しました

-

2017.4.1

4月号をアップしました

-

2017.3.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第6回 初めてのQSOの思い出 with グリーンのアクアパッツァ、FB Monthly Fashion/第3回 ピンクを使ったコーディネート、子供の無線教室/第3回 「電波はどうやって伝わるの?」を掲載しました

-

2017.3.1

3月号をアップしました

-

2017.2.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第5回 FB Girlsの試験の思い出 withウマ辛和風スープ、FB Monthly Fashion/第2回 デニムと明るめニットのコーディネートを掲載しました

-

2017.2.1

2月号をアップしました

-

2017.1.16

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第4回 YLハムを増やす秘策とは?! withおなかにやさしいお料理、【新連載】FB Monthly Fashion/第1回 アウター別おすすめコーディネート(ライダース・ノーカラー・ダッフル)を掲載しました

-

2017.1.5

1月号をアップしました

-

2016.12.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第3回 YLハムの行く年来る年 with ブイヤベースの洋風お鍋を掲載しました

-

2016.12.1

12月号をアップしました

-

2016.11.15

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(後編)!、What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第2回 YLハムの悩み解決!with サケのフレンチトーストを掲載しました

-

2016.11.1

11月号をアップしました

-

2016.10.17

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(前編)!、【新連載】What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第1回 FB GirlsのプライベートQSO with 土瓶蒸しのリゾットを掲載しました

外部リンク

アマチュア無線関連機関/団体

各総合通信局/総合通信事務所

アマチュア無線機器メーカー(JAIA会員)

次号は 12月 1日(木) に公開予定