ジャンク堂

第5回 オペアンプ入門(5)

オペアンプ入門5回目です。今回は少しややこしい話しになりました。

前回、オペアンプのマイナス入力端子と出力端子にコンデンサを入れると発振する恐れがあると説明をしました。今回はその理由をもう少し詳しく説明したいと思います。この内容はオペアンプに限らずNFBを掛けている増幅器全般に当てはまります。

NFBとPFB

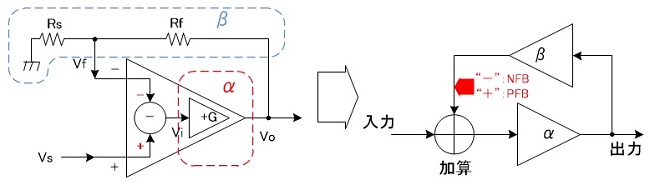

以前に下図左のようなオペアンプについてのブロック図を紹介しました。この図をもう少し一般化すると下図右のようになります。

図右は閉ループ回路と呼ばれる回路の一般的なブロック図で、オペアンプ回路は閉ループ回路です。ここでβと書かれているブロックが出力を入力に戻すフィードバック(帰還)の経路です。このように出力が入力に戻りループ状となる回路を閉じたループ、閉ループ(Closed Loop)回路と呼びます。もし、このループがどこかで途切れている場合は開ループ(Open Loop)となります。

閉ループ回路ではβからの出力の位相がマイナス(入力と反対の位相)の時にNFBとなり、プラス(入力と同じ位相)の時にPFBとなります。加算と書かれたマル印の十字は足し算を意味しています。

注) NFB: Negative Feedback 負帰還

PFB: Positive Feedback 正帰還

αに入力された信号は(αのゲイン)×(βのゲイン)倍されてβから出力されます。

余談ですが、無線機のブロック図でミキサーを〇に✕のマークで表しますが、これは2つの入力を掛け算するという意味で、ミキサー回路は掛け算器になります。

オペアンプの場合のβはRsとRfによる抵抗の分圧回路でゲインは1以下になります。また、βに相当する回路で位相は変化しません。加算回路に相当する部分が引き算(差動アンプ)となっているので結果としてβからの出力が入力信号と同位相の時に減算されることになります。言葉で書くと分かりにくいですが、上図の左右を併せて見て頂ければ分かるかと思います。

さて、図右で信号の流れを見て頂ければβの出力が入力信号と同位相で加算されるとαへ入る信号が入力信号より大きくなることがわかると思います。その結果、αの出力も大きくなり、連れてβの出力も大きくなり・・・、を繰り返して出力がどんどん大きくなっていきます。これがPFBの状態です。

もし、このPFBの状態でβの出力が入力信号より大きい時、つまりαとβのゲインを掛けた時のゲインが1以上あると入力信号が途中で無くなっても発振が継続する条件が整います。ただし、発振が起きるためには最初にこの条件が整う周波数の信号が外部から加えられる必要があります。発振にはきっかけが必要で、実際の回路では部品のノイズや電源投入時の過度的な電圧変動(ショック)などがそのきっかけになります。また、ゲインが1未満であれば発振は継続しませんがリンギングとなります。

オペアンプの発振はNFBのつもりが高い周波数でPFBに変化することから起こります。これは周波数が高くなるとループ内で位相が変化するためです。

積分回路の振幅特性と位相特性

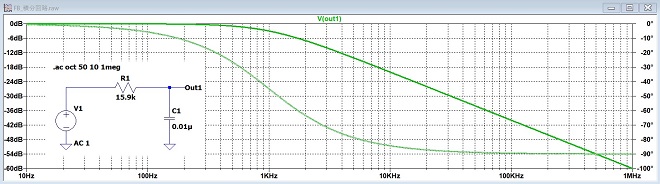

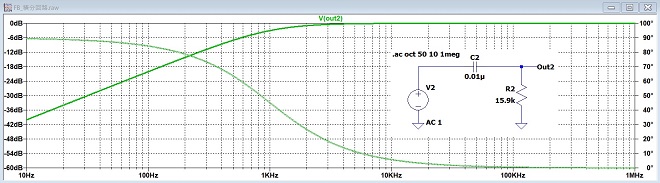

ここで積分回路(LPF)と微分回路(HPF)の話しになります。下のLTspiceのシミュレーション結果をご覧ください。今回のグラフでは振幅(電圧)レベルと同時に位相偏移もグラフに描かれています。fc=1kHzとなるように抵抗は中途半端な値になっています。上が積分回路で下が微分回路です。

各々のグラフでは濃い色が振幅(電圧)レベルで、少し薄い色が位相特性です。

このように周波数に対する振幅特性と位相特性を一つのグラフに表したものをボード線図(Bode Plot)と呼びます。日本語ではボーデ線図と表記されることも多いです。

CR1段の積分回路では-3dBの点で位相は45°の遅れとなっています。さらに周波数が高くなると6dB/octでゲインは低下を続けますが、位相は最大90°遅れまでであることが分かります。逆に微分回路では周波数が低くなるとゲインが低下し、位相は最大90°まで進んでいます。積分回路と微分回路は振幅だけでなく位相も正反対の特性です。

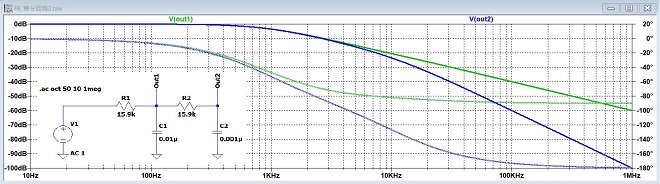

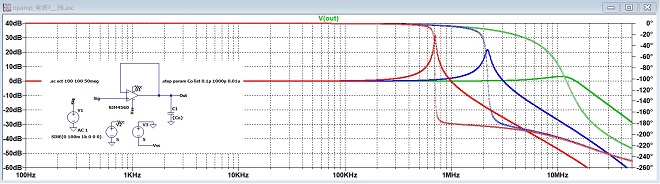

ここからはオペアンプの発振の主要因となる積分回路に話しを絞ります。下の図は積分回路を2段重ねた特性です。定数から計算して頂くと分かりますが1段目の積分回路のfcが1kHzで2段目は10kHzになっています。緑の線が1段目の出力で青の線が2段目の出力です。

振幅特性(濃い線)をみると1段目の出力(Out1)に対して2段目の出力(Out2)は10kHzから減衰の度合いが12dB/octに変化します。

ここで注目して頂きたいのは位相の遅れで、CR1段の積分回路では最大90°遅れまでですが、2段目の出力はでは最大180°まで遅れが生じています。当たり前といえば当たり前で、3段だと270°になります。

オペアンプのボード線図

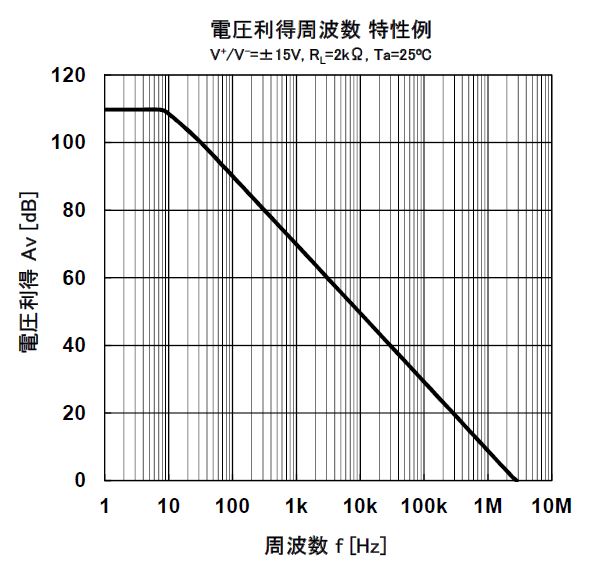

さて、以上を踏まえてオペアンプの話しに戻ります。2回目に紹介したオペアンプの裸ゲインの特性が再登場します。下のグラフがそれです。このグラフを引用したときはNJM4558の開ループ(オープンループ)の特性として紹介しました。

グラフでは10Hzから上の周波数でゲインが6dB/octで減少しています。このグラフには位相特性が載っていないのですが、ゲインが大きいことを除けばこの特性は積分回路と同じになります。つまりオペアンプはゲインを持った積分回路とみなせ、位相特性も同様に最大90°までの遅れとなります。多くのオペアンプがこのようにゲインが0dBになる周波数まで6dB/octで低下する特性になっています。

なお、グラフではゲインが0dBまでしか描かれていませんが実際のオペアンプではゲイン0dBとなる周波数より高い周波数では12dB/octや18dB/octとなって位相は90°以上変化します。これはオペアンプの内部には複数の積分回路を構成する要素があるためです。最近はあまり見かけませんが一部のオペアンプでは周波数特性を伸ばすためにゲインが10dB程度のところで12dB/octに変化しているモノもあります。このようなオペアンプはデータシートにゲインを20dB以上で使用するように、などという注意書きがあります。

さて、RfとRsの抵抗だけのフィードバック経路では位相が変化しないことと、ゲイン0dB以上の周波数でオペアンプによる位相の変化が最大で90°までだとNFBを掛けても発振はしません。オペアンプの周波数とゲインの関係がこのようになっているのは、NFBを掛けたときに発振しないようにするためです。

オペアンプが発振する理由

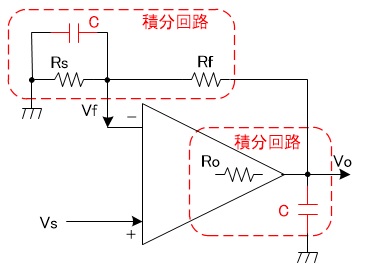

ところが、もしループのどこかにもう1段積分回路が入ると位相は最大180°まで遅れてしまいます。例えば、マイナス入力端子とアースの間にコンデンサを入れるとRfとコンデンサで積分回路が出来上がります。(正確にはRf//Rsですが) また出力端子に入れるとどうでしょう? オペアンプの出力インピーダンスはほぼ0Ωと説明しましたが、これはNFBが正常に掛かっていることが前提です。もしNFBが無ければ数十Ω程度のインピーダンスが存在します。このインピーダンスと出力端子に接続したコンデンサで、やはり積分回路が出来上がってしまいます。これを表したのが下の図です。

もっとも、フィードバック経路に積分回路を一つ入れただけであれば最大でも位相遅れは180°までです。また、コンデンサの容量が小さければ位相遅れが180°になる周波数が高いため、ゲインが下がって1以下となれば発振には至りません。但し、位相遅れが180°に近くなるとその周波数近辺にピークが生じ、矩形波を入力するとリンギングが発生します。しかし実際のオペアンプは内部に複数の積分回路の要素を持っているのでもう少し位相の動きは大きくなります。

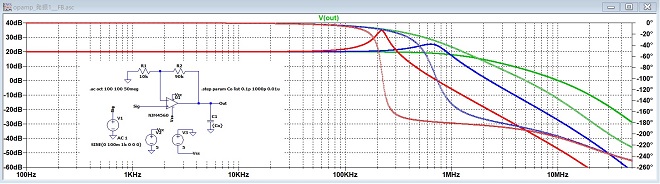

ここで、出力端子にコンデンサを接続した場合をシミュレーションしてみました。

NJM4560のゲインを20dB(10倍)に設定し、出力にCo(C1)というコンデンサを0.1pF(緑)/ 1000pF(青)/ 0.01uF(赤)と変化させた時の周波数特性です。少し薄い色の線が位相です。1000pFでは少しピークが出来ており、0.01uFではかなり大きなピークが出来ています。

なお、このグラフをみると高域で位相は180°以上変化しているのでオペアンプ自体に積分要素が2つ以上あることが分かります。

さて、このボード線図の見方ですが、ゲインが0dBの時の位相を確認します。あるいは位相が180°遅れの点のゲインを確認します。発振条件は位相が180°のときにゲインが1(0dB)以上かどうかですが、別の見方をするとゲインが1になったときに位相が180°まで行っているかどうかでもあります。Coが0.1pFではゲインが0dBのときの位相は135°程度の遅れなので発振する180°に対して45°程度の余裕があります。これを位相余裕度と呼びます。しかし、Coが1000pFの時は175°程度まで遅れており余裕度がほとんどありません。Coが0.1uFの時はほぼ180°に近くなっています。

次にゲイン設定を0dB(1倍)にしてみます。この回路はボルテージフォロアと呼ばれる回路でバッファ回路として良く使われますが負帰還の量がもっとも多い回路です。

出力のCoが0.1pFの状態でも少しピークが出始めていますが位相余裕度はあります。しかし1000pFや0.01uFでははっきりとピークが出て、位相余裕度もほとんどありません。ギリギリ発振するかしないかの境目のようです。仮に発振しなくてもこのような特性はアンプとしてはかなり不安定であるといえるでしょう。

これらのピークは発振、あるいはリンギングにつながります。アンプはゲインを上げると発振しやすくなると思われがちですが、オペアンプはゲイン設定を下げると発振しやすくなります。ゲイン設定が低いということはフィードバック量が多いということで、NFB経路での位相変化に敏感になります。

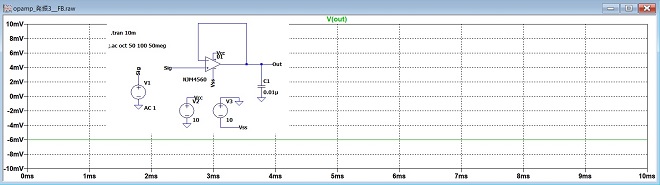

さて、このような条件では実際に発振するのでしょうか? ボード線図をみる限り、最も不安定(発振しそう)なゲイン0dBでCoが0.01uFのときをシミュレーションして出力をみました。

少し分かり難いですが-6mVに緑の線があり、これが出力波形です。とくに発振の様子は見られません。-6mVはオフセットによるズレです。

実はシミュレーションでは発振の再現が難しいのです。部品モデルの精度などの問題もあるかと思いますがシミュレーションの世界にはノイズなどが無く発振が始まるきっかけが無いためでもあるようです。そもそも発振は条件を満たす周波数に何らかの信号があって初めてスタートします。従って、シミュレーション上で発振しないようでも実回路では発振します。シミュレーション上ではボード線図から回路の安定性を判断した方が良さそうです。

実際に試してみました

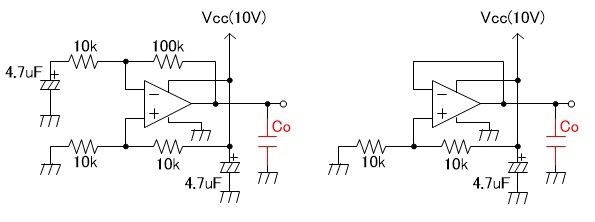

そこで実際の回路だとどうか確認をしてみました。下図のようなゲイン20.8dB(11倍)とゲイン0dB(1倍)のボルテージフォロアをブレッドボード上に組んでみました。両電源は面倒なので単電源で組んでいます。またCoは無し/1000pF/0.01uFと変えてみました。

20.8dB回路 0dB回路

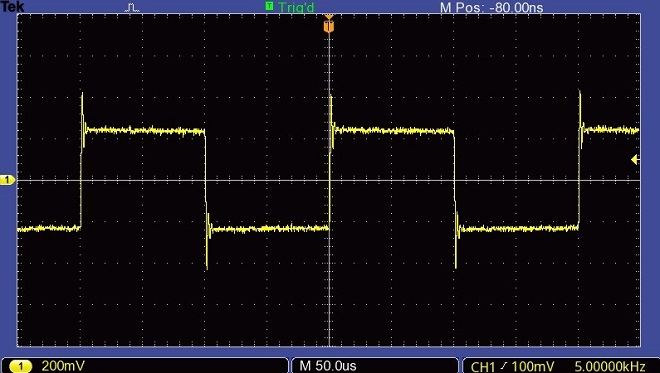

私が組んだブレッドボード上ではゲインが20.8dBの場合はいずれのコンデンサでも無信号で出力が出るというような発振は見られませんでした。ただ、Coが0.01uFのときは下のようなリンギングが見られますが、1000pFではリンギングもほとんど見られませんでした。

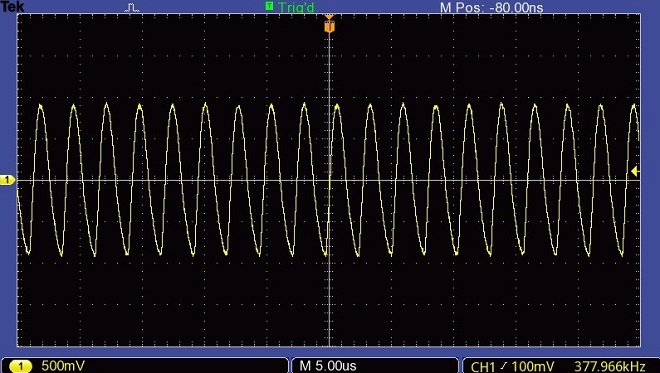

次にゲインが0dBのボルテージフォロアの場合ですが、Coが1000pFの時は発振が見られませんでしたが、0.01uFの時に発振が見られました。下の図はボルテージフォロアで出力に0.01uFを接続したときの出力波形です。入力信号はありません。

リンギングの波形や発振波形の周期をみてシミュレーションと異なるようだったので、G=10で0.01uFの時に正弦波を入力して周波数をスイープしてみました。先のシミュレーションでは200kHzより少し上に15dBのピークが出ていますが、実回路では340kHz付近に7dB程度のピークでした。またG=1の時の発振周波数も380kHzと、シミュレーションのピークとはかなり異なります。この差はシミュレーションモデルと実際のNJM4560との差なのか、実物のNJM4560のバラツキなのかは分かりません。あるいは私のミスなのかも知れませんが、私が確認したNJM4560とシミュレーションモデルとは差があるようです。(シミュレーションモデルにはJRCがPSpice用に公開しているものを使用しています) なお、実回路での自励発振周波数がシミュレーション上のピーク周波数より低いのはスルーレートの影響を受けているのかも知れません。

ブレッドボードの結果から“なんだ、現実はコンデンサを入れても思っていたよりは発振しないじゃないか”と思われるかも知れません。私はそのように思いました。(苦笑) ただ自励発振に至らなくても周波数特性に大きなピークができるとアンプとしては不安定であることは間違いありません。私は今までオペアンプが発振しているのを幾度も見てきましたので、オペアンプは意外と発振しやすく、また発振していることに気づきにくいものだと思っています。

結局、どうするのか

ローム社の資料などではボード線図上で、位相余裕度は35°以上、あるいは位相が180°になるときのゲインは-7dB以下を推奨されています。この数値はオペアンプに限らず一般的に閉ループ回路で推奨される値です。オペアンプ自体の位相余裕度は45°~60°程度で作られているそうですが、ものによって様々です。出力端子などにコンデンサを入れた場合の発振のしやすさは元々のオペアンプの位相余裕度も関係します。

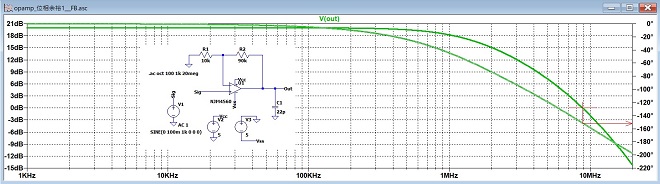

実回路と差はあるようですがNJM4560のシミュレーションで確認した結果ではゲインが20dBの場合であっても1000pFを出力端子に接続すると位相余裕度の面でNGでした。どの程度まで良さそうかを懲りずにシミュレーションでみると、ゲイン20dBの場合、22pFで位相遅れが約150°で位相余裕度は30°程度になります。(下のグラフの右端、赤線部分参照) 実際のNJM4560ではどうなのか、位相余裕度を簡単に確認する方法が私にはないのでなんとも言えません。

前回、出力端子に入れるコンデンサは数十pF程度までと脅しました。これはかなりコンサバな値かも知れませんがオペアンプの種類を特定せずに、一般的に安定と言われる位相余裕度に納めようとすると、やはりこの程度の容量になると思います。

また、実回路で位相余裕度の測定が難しいことも安定である範囲を特定しにくくしています。直接位相余裕度が分かる測定器も世の中にはありますがあまり一般的ではないと思います。アマチュア的には測定が難しい位相余裕度の値よりも実際に組んだ回路でリンギングや周波数特性上のピークを測定して、僅かなリンギングや数dB程度のピークであればOKとするのもひとつかと思います。それであってもオシロスコープや発振器などの測定器が必要になります。それらが無ければ出力端子やマイナス入力端子にコンデンサを直接入れることは止めておくべきでしょう。そうすれば最近のオペアンプは安定に動作してくれます。

ということで、出力端子とマイナス入力端子にコンデンサを入れるな! とクドクドと書いてきましたが、次回ももう少し発振についての話しをしたいと思います。

なお、位相余裕度と周波数特性のピークには関連がありますが、何dBのピークの時に位相余裕度がいくら、、とは前提条件を整えないと一概に言えません。先のゲイン10倍で22pFを負荷に接続したグラフよりゲイン1のボルテージフォロアのグラフで出力のコンデンサが0.1pFのときの方がピークは大きいことからも分かるかと思います。

単電源増幅回路の注意点

さて、前回(第4回)の終わりの方で、いままで紹介している単電源の非反転増幅回路はあまり良くないと述べましたので、その話しをしたいと思います。それはプラス入力端子に電圧を与える回路の部分です。今まで何度も出てきている単電源増幅回路では電源ラインから抵抗で分圧した電圧を直接プラス入力端子に加えています。机上ではそれで良いのですが、実際に回路を組む場合、この回路では電源ラインのノイズも抵抗で分圧されてプラス入力端子に加わります。そのため電源ラインにノイズがあるとそれを増幅してしまいます。

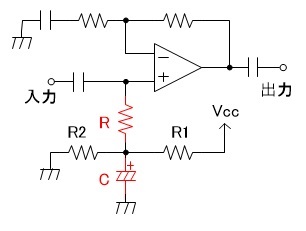

そこで、下の回路のようにRとCを追加します。

R1とR2による分圧回路とコンデンサCによるノイズ除去を行った上で抵抗Rを介してプラス入力端子に電圧を加えます。Rの値は数k~数十kΩであれば適当に選べます。この抵抗値がAF周波数における入力インピーダンスになります。ノイズ除去を行うR1, R2, Cによるリップルフィルタは、R1とR2の並列接続抵抗値をRpとすると、いつもの f=1/(2πCRp) の式でカットオフ周波数が求まり、高域に向かって6dB/octでノイズが減衰します。fcは数Hzから数十Hzに選べば無難です。ただし、電源ラインにもパスコンを入れて電源ラインのノイズを抑えておくことも大切です。また反転増幅の場合も同様の処理が必要ですが上図のRは必要ありません。

オペアンプの重要な特性のひとつに電源電圧変動除去比(PSRR: Power Supply Rejection RatioやSVR: Supply Voltage Rejectionともいう)があり、電源電圧除去比とも呼ばれます。これは、電源電圧の変動の影響を受けない度合いのことで、オペアンプは電源ラインにノイズがあっても出力には表れにくくなっています。しかし、せっかく電源ラインのノイズの影響を受けにくいオペアンプであっても抵抗を通して入力端子に電源ラインのノイズが入って来ると台無しです。単電源で使用する場合のプラス入力端子に与える電圧にはくれぐれもノイズが無いように注意が必要です。

それでは73&88

<記事中のグラフは下記より引用>

・NJM4558 データシート: 新日本無線株式会社 公開データシート

ジャンク堂 バックナンバー

- 第24回 オペアンプ入門(24)

- 第23回 LTspiceのススメ(後編)

- 第22回 LTspiceのススメ(前編)

- 第21回 (今日のジャンク)AZDEN DX-327というダイナミックマイクを復活させる

- 第20回 エクセルを使って空芯コイルのインダクタンスを計算する

- 第19回 電波防護指針に基づく電界強度を計算してみる

- 第18回 電子回路の放熱

- 第17回 秋月電子のレベルメーターキットを作る

- 第16回 FT8とALC、そしてスプラッタ

- 第15回 オシロスコープの50Ω終端器

- 第14回 差動アンプ 他 オペアンプ入門(14)

- 第13回 アクティブフィルタ オペアンプ入門(13)

- 第12回 RIAAとJIS A特性の等価雑音帯域幅とLTspice(オペアンプとノイズ おまけ編) オペアンプ入門(12)

- 第11回 オペアンプとノイズ(後半) オペアンプ入門(11)

- 第10回 オペアンプとノイズ(前半) オペアンプ入門(10)

- 第9回 オペアンプ入門(9)

- 第8回 オペアンプ入門(8)

- 第7回 オペアンプ入門(7)

- 第6回 オペアンプ入門(6)

- 第5回 オペアンプ入門(5)

- 第4回 オペアンプ入門(4)

- 第3回 オペアンプ入門(3)

- 第2回 オペアンプ入門(2)

- 第1回 ジャンク堂開店。オペアンプ入門(1)

お知らせ

-

2022.11.15

11月号後半の記事をアップしました

-

2022.11.1

11月号の記事をアップしました

-

2022.10.17

10月号後半の記事をアップしました

-

2022.10.3

10月号の記事をアップしました

-

2022.9.15

9月号後半の記事をアップしました

-

2022.9.1

9月号の記事をアップしました

-

2022.8.15

8月号後半の記事をアップしました

-

2022.8.1

8月号の記事をアップしました

-

2022.7.15

7月号後半の記事をアップしました

-

2022.7.1

7月号の記事をアップしました

-

2022.6.15

6月号後半の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JL3ZGL」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2022.6.1

6月号の記事をアップしました

6月4日(土)、JH1CBX/3が14MHz SSBに初オンエアします。 入感がありましたらぜひお声がけください。 -

2022.5.16

5月号後半の記事をアップしました

-

2022.5.2

5月号の記事をアップしました

5月14日(土)、JL3ZGLはオペレーターにMasacoさんを迎えHAMtte交信パーティに 参加します。詳しくは4月号のニュースをご確認ください。 -

2022.4.15

4月号後半の記事をアップしました

-

2022.4.1

4月号の記事をアップしました

-

2022.3.15

3月号後半の記事をアップしました

-

2022.3.1

3月号の記事をアップしました

-

2022.2.15

2月号後半の記事をアップしました

-

2022.2.1

2月号の記事をアップしました

-

2022.1.17

1月号後半の記事をアップしました

-

2022.1.5

1月号の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JA3YUA」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2021.12.15

12月号後半の記事をアップしました

-

2021.12.1

12月号の記事をアップしました

-

2021.11.15

11月号後半の記事をアップしました

-

2021.11.01

2021年11月号の記事をアップしました

-

2021.10.15

10月号後半の記事をアップしました

-

2021.10.01

2021年10月号の記事をアップしました

-

2021.09.15

9月号後半の記事をアップしました

-

2021.09.01

2021年9月号の記事をアップしました

-

2021.08.16

8月号後半の記事をアップしました

-

2021.08.02

2021年8月号の記事をアップしました

-

2021.07.15

7月号後半の記事をアップしました

-

2021.07.01

2021年7月号の記事をアップしました

-

2021.06.15

6月号後半の記事をアップしました

-

2021.06.01

2021年6月号の記事をアップしました

-

2021.05.17

5月号後半の記事をアップしました

-

2021.05.06

2021年5月号の記事をアップしました

-

2021.04.15

4月号後半の記事をアップしました

-

2021.04.01

2021年4月号の記事をアップしました

連載記事 Masacoの「むせんのせかい」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.15

3月号後半の記事をアップしました

連載記事「今月のハム」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.01

2021年3月号の記事をアップしました

-

2021.02.15

2月号後半の記事をアップしました

-

2021.02.01

2021年2月号の記事をアップしました

-

2021.01.15

1月号後半の記事をアップしました

-

2021.01.05

2021年1月号の記事をアップしました

-

2020.12.15

12月号後半の記事をアップしました

-

2020.12.01

2020年12月号の記事をアップしました

-

2020.11.16

11月号後半の記事をアップしました

-

2020.11.02

2020年11月号の記事をアップしました

-

2020.10.15

10月号後半の記事をアップしました

-

2020.10.01

2020年10月号の記事をアップしました

-

2020.09.15

9月号後半の記事をアップしました

-

2020.09.01

2020年9月号の記事をアップしました

-

2020.08.17

8月号後半の記事をアップしました

-

2020.08.03

2020年8月号の記事をアップしました

-

2020.07.15

7月号後半の記事をアップしました

-

2020.07.01

2020年7月号の記事をアップしました

-

2020.06.15

6月号後半の記事をアップしました

-

2020.06.01

2020年6月号の記事をアップしました

-

2020.05.01

2020年5月号の記事をアップしました

-

2020.04.15

4月号後半の記事をアップしました

-

2020.04.01

2020年4月号の記事をアップしました

-

2020.03.16

3月号後半の記事をアップしました

-

2020.03.09

JARD、eラーニングでのアマチュア無線国家資格取得を呼び掛けるお知らせを、臨時休校で自宅待機中の小中高生に向けて発表。詳しくはこちら。

-

2020.03.02

2020年3月号の記事をアップしました

-

2020.02.17

2月号後半の記事をアップしました

-

2020.02.03

2020年2月号の記事をアップしました

-

2020.01.15

1月号後半の記事をアップしました

-

2020.01.06

2020年1月号の記事をアップしました

-

2019.12.16

12月号後半の記事をアップしました

-

2019.12.02

2019年12月号の記事をアップしました

-

2019.11.15

11月号後半の記事をアップしました

-

2019.11.01

2019年11月号の記事をアップしました

-

2019.10.15

10月号後半の記事をアップしました

-

2019.10.01

2019年10月号の記事をアップしました

-

2019.09.17

9月号後半の記事をアップしました

-

2019.09.02

2019年9月号の記事をアップしました

-

2019.08.16

8月号後半の記事をアップしました

-

2019.08.01

2019年8月号の記事をアップしました

-

2019.07.16

7月号後半の記事をアップしました

-

2019.07.01

2019年7月号の記事をアップしました

-

2019.06.17

6月号後半の記事をアップしました

-

2019.06.01

2019年6月号の記事をアップしました

-

2019.05.20

5月号後半の記事をアップしました

-

2019.05.07

2019年5月号の記事をアップしました

-

2019.04.15

4月号後半の記事をアップしました

-

2019.04.01

2019年4月号の記事をアップしました

-

2019.03.15

3月号後半の記事をアップしました

-

2019.03.01

2019年3月号の記事をアップしました

-

2019.02.15

2月号後半の記事をアップしました

-

2019.02.01

2019年2月号の記事をアップしました

-

2019.01.18

1月号後半の記事をアップしました

-

2019.01.07

2019年1月号の記事をアップしました

-

2018.12.17

12月号後半の記事をアップしました

-

2018.12.01

2018年12月号の記事をアップしました

-

2018.11.15

11月号後半の記事をアップしました

-

2018.11.01

2018年11月号の記事をアップしました

-

2018.10.15

10月号後半の記事をアップしました

-

2018.10.01

2018年10月号の記事をアップしました

-

2018.09.15

9月号後半の記事をアップしました

-

2018.09.01

2018年9月号の記事をアップしました

-

2018.08.17

8月号後半の記事をアップしました

-

2018.08.01

2018年8月号の記事をアップしました

-

2018.07.17

7月号後半の記事をアップしました

-

2018.07.02

2018年7月号の記事をアップしました

-

2018.06.15

6月号後半の記事をアップしました

-

2018.06.01

2018年6月号の記事をアップしました

-

2018.05.15

5月号後半の記事をアップしました

-

2018.05.01

2018年5月号の記事をアップしました

-

2018.04.16

4月号後半の記事をアップしました

-

2018.04.02

2018年4月号の記事をアップしました

-

2018.03.15

3月号後半の記事をアップしました

-

2018.03.01

2018年3月号の記事をアップしました

-

2018.02.15

2月号後半の記事をアップしました

-

2018.02.01

2018年2月号の記事をアップしました

-

2018.01.15

1月号後半の記事をアップしました

-

2018.01.05

2018年1月号の記事をアップしました

-

2017.12.15

12月号後半の記事をアップしました

-

2017.12.1

12月号をアップしました

-

2017.11.15

11月号後半の記事をアップしました

-

2017.11.1

11月号をアップしました

-

2017.10.16

10月号後半の記事をアップしました

-

2017.10.2

10月号をアップしました

-

2017.9.15

What a healthy time! ~健康を応援する特別なお料理~/第3回 食物繊維たっぷり! 海藻の和風リゾット、FB Monthly Fashion/第9回 秋っぽい柄&色コーデ、子供の無線教室/第9回 「アンテナの形や大きさに注目!!」を掲載しました

-

2017.9.4

<速報>ハムフェア2017を掲載しました

-

2017.9.1

9月号をアップしました

-

2017.8.17

What a healthy time! ~健康を応援する特別なお料理~/第2回 和風のポトフ 納豆ソース添え、FB Monthly Fashion/第8回 夏のお出かけコーデ、子供の無線教室/第8回 「無線機にはどんなものがあるの?」を掲載しました

-

2017.8.1

8月号をアップしました

-

2017.7.18

What a healthy time! ~健康を応援する特別なお料理~/第1回 メロンの冷製スープ ナッツのアイスクリームのせ、FB Monthly Fashion/第7回 コットンTシャツコーデとボーイズコーデ、子供の無線教室/第7回 「電波はどうやって海外や宇宙に届くの?」を掲載しました

-

2017.7.1

7月号をアップしました

-

2017.6.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第9回 FB Girlsの野望 with ムースと甘エビのタルタル、FB Monthly Fashion/第6回 雨の日コーデと親子コーデ、子供の無線教室/第6回 「電波はいろいろなところで大活躍!!」を掲載しました

-

2017.6.1

6月号をアップしました

-

2017.5.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第8回 番外編 春うらら♪豪華弁当でお花見、FB Monthly Fashion/第5回 ブラウス&シャツを使ったコーディネート、子供の無線教室/第5回 「周波数によって変わる、電波の特徴」を掲載しました

-

2017.5.1

5月号をアップしました

-

2017.4.17

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第7回 ARDFの思い出 with 2種類のソースのカルボナーラ、FB Monthly Fashion/第4回 Gジャンを使ったコーディネート、子供の無線教室/第4回 「電波の性質を覚えよう」を掲載しました

-

2017.4.1

4月号をアップしました

-

2017.3.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第6回 初めてのQSOの思い出 with グリーンのアクアパッツァ、FB Monthly Fashion/第3回 ピンクを使ったコーディネート、子供の無線教室/第3回 「電波はどうやって伝わるの?」を掲載しました

-

2017.3.1

3月号をアップしました

-

2017.2.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第5回 FB Girlsの試験の思い出 withウマ辛和風スープ、FB Monthly Fashion/第2回 デニムと明るめニットのコーディネートを掲載しました

-

2017.2.1

2月号をアップしました

-

2017.1.16

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第4回 YLハムを増やす秘策とは?! withおなかにやさしいお料理、【新連載】FB Monthly Fashion/第1回 アウター別おすすめコーディネート(ライダース・ノーカラー・ダッフル)を掲載しました

-

2017.1.5

1月号をアップしました

-

2016.12.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第3回 YLハムの行く年来る年 with ブイヤベースの洋風お鍋を掲載しました

-

2016.12.1

12月号をアップしました

-

2016.11.15

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(後編)!、What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第2回 YLハムの悩み解決!with サケのフレンチトーストを掲載しました

-

2016.11.1

11月号をアップしました

-

2016.10.17

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(前編)!、【新連載】What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第1回 FB GirlsのプライベートQSO with 土瓶蒸しのリゾットを掲載しました

外部リンク

アマチュア無線関連機関/団体

各総合通信局/総合通信事務所

アマチュア無線機器メーカー(JAIA会員)

次号は 12月 1日(木) に公開予定