今更聞けない無線と回路設計の話

【テーマ1】三角関数のかけ算と無線工学

第14話

PLLの動作原理と代表構成

2023年4月3日掲載

第13話ではPLLの代表用途について少し触れた上で、理想のサイン波と実際のサイン波の違いとして位相雑音、周波数偏差について解説しました。第14話はPLLが具体的にどうやって位相雑音を除去したり、周波数偏差のない周波数変換(周波数合成)を行っているのかについて解説したいと思います。

1. PLLの基本構成と動作

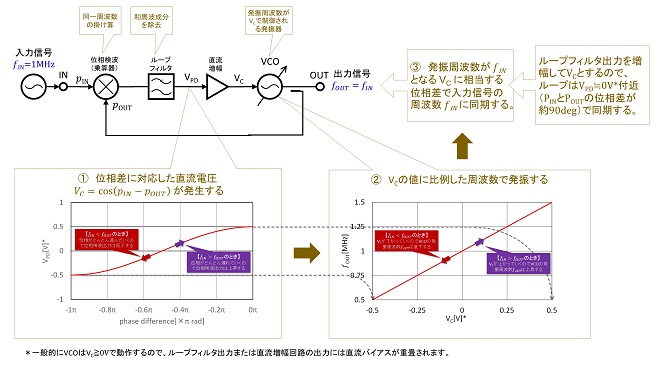

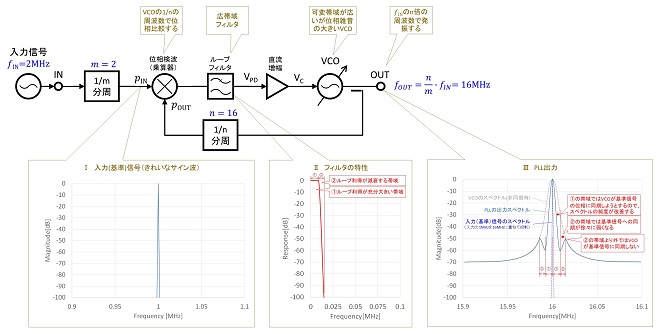

図1にPLLの基本構成と動作を示します。PLLとはPhase Locked Loopの略で入力信号の位相に同期する回路を示します。

(1) PLLの基本構成

PLLの用途は様々ですが、どのような用途のPLLであっても必須となるのは以下に示す3つの機能ブロックです。

- ①位相検波器: 入力信号と出力信号の位相差を検出します。位相検波には複数の方式がありますが、アナログPLLの場合は第12話で解説した乗算回路で実現されます。

- ②ループフィルタ: アナログ乗算器が出力する2倍波成分の除去とループの応答特性を決定するLPFです。

- ③VCO: 出力信号を生成する発振器です。VCOはVoltage Controlled Oscillator(電圧制御発振器)の略で制御電圧VCに比例した周波数で発振する発振器です。

PLLに入力された信号は位相検波器の片方の入力端子に入力されます。位相検波器の出力はループフィルタを介してVCOの制御端子に接続され、VCOの出力が位相検波器のもう一方の入力端子にフィードバックされます。一般的な用途ではVCOの出力信号を抽出してPLLの出力信号とします。なお、図1に示すようにループゲインを確保するために位相検波器とVCOの間に直流増幅器を挿入する場合もあります。

(2) PLLの基本動作

説明を簡単にするために、図1においてVCOは入力周波数とほぼ同じ周波数で発振していると仮定します。入力端子(IN)にある周波数(図では1MHz)のサイン波を入力すると、位相検波器(乗算器)は入力されたサイン波の位相𝑝INとVCOの発振信号の位相𝑝OUTの位相差に相当する直流電圧、ならびに両者の和周波成分(2倍波)を出力します。この出力から後段のLPFで和周波成分を除去することにより、位相差情報VPDを得ます(図1の①)。位相差情報VPDは後段の直流増幅器で増幅されてVCOの制御電圧VCとなります。VCOはVCに応じた周波数で発振します(図1の②)。そしてVCOの出力は位相検波器にフィードバックされます。位相検波器の出力とVCOの発振周波数の関係を見ると、入力されたサイン波の位相𝑝INよりもVCOの発振信号の位相𝑝OUTの位相が進んだとき、すなわちVCOの発振周波数が入力周波数より高くなろうとする時に位相差情報VPDは下降し、VPDの下降に伴ってVCも下降し結果VCOの発振周波数が下降するという動作になっています※1。この結果VCOの発振信号(サイン波)は入力されたサイン波との位相差が一定になるように同期します(図1の③)。位相差が一定値に保たれると言うことは入力信号の周波数とVCOの発振周波数は等しい値だと言うことになります。無線通信機で使用される一般的なPLL回路ではVCOの出力信号をPLLの出力信号として取り出しています。

※1 第12話の図5に示したように、アナログ乗算器で位相検波した場合の出力電圧と入力位相差の関係は、位相差−π~0[rad]の範囲では右肩上がりの傾斜、位相差0~+π[rad]の範囲では左肩上がりの傾斜となり、位相遅れ/進みと電圧上昇/降下の関係が逆転します。従って、アナログ位相検波器を使用した実際のPLLでは起動時に負帰還/正帰還の状態を繰り返しながら、VCOの発振周波数が入力周波数にそろい、かつ位相検波器とVCOの制御電圧の関係が負帰還となったところでロックするという課程を辿ります。なお無線通信機のPLLシンセサイザで一般的なデジタル位相検波器については後日解説します。

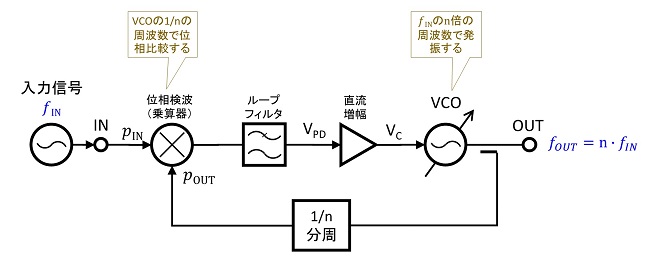

(3) 周波数を逓倍する仕組み

図2に示すようにVCOから位相検波器へのフィードバックループに1/nの分周器を挿入すると、VCOの発振出力と入力周波数が位相同期する為には、VCOは入力周波数のn倍の周波数で発振する必要があります。𝑓INと1/n×𝑓OUTが位相同期している状態においては、𝑓INと𝑓OUTの比は正確に「n」という値になり、入力信号の周波数がn倍に逓倍されたことになります。

2. 周波数領域で見たPLLの動作

PLLは入力信号に位相同期して発振するオシレータと考えることが可能です。「入力信号に位相同期する」というのは時間軸上で表現した動作説明ですが、これを周波数軸上で見ると以下のように整理することが可能です。

- ①VCOが入力信号に位相同期すると、結果的に入力信号の周波数にVCOの発振周波数が同期する。すなわち入力信号の最大スペクトル(=瞬時周波数の時間平均値)とVCOのピークスペクトルが周波数軸上で一致する。

- ②VCO単体の位相雑音レベルよりも、入力信号の位相雑音レベルが大きい場合、VCOが入力信号に位相同期すると、VCOの位相雑音レベルは単体のそれよりも上昇する。

- ③VCO単体の位相雑音レベルよりも、入力信号の位相雑音レベルが小さい場合、VCOが入力信号に位相同期すると、VCOの位相雑音レベルは単体のそれよりも低下する。

このうち①と②の特性を利用して入力信号の位相雑音を抑制するのが「PLLフィルタ」、「ジッタアッテネータ」などと呼ばれる回路、①と③の特性を用いてXtalオシレータなどの周波数偏差の小さい高純度源振から周波数合成を行うのが「PLLシンセサイザ」と呼ばれる回路になります。

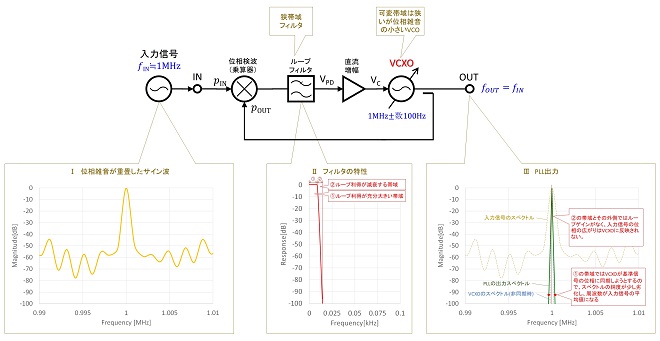

3. PLLフィルタ(位相雑音抑制フィルタ)

この回路は無線通信機よりも、有線伝送系のジッタアッテネータ、またはデジタル回路のクロック信号のジッタフィルタとしてよく利用されるアプリケーションです。図3に動作の概要を示します。

PLLを位相雑音抑圧フィルタの目的で使用する場合、VCOにはVCXO(周波数可変型水晶発振器)など、スペクトル純度の高い発振回路を適用し、ループフィルタの通過帯域幅は極力狭く設計します。このPLLは2章に記載した「VCO単体の位相雑音レベルよりも、入力信号の位相雑音レベルが大きい」状態のPLLであり、VCOの位相雑音レベルが入力信号に位相同期することで上昇するという動作になります。

周波数軸上で見ると、PLLの入力には図3の吹出しⅠに示すような位相雑音が重畳したサイン波が入力され、位相比較器(乗算器)でVCXOの出力するサイン波(吹出しⅢ)と位相比較(同一周波数の乗算)されます。両者とも純粋なサイン波ではなく、ある帯域幅を持ったスペクトルなので、両者の積(差周波成分)は直流のみにはならず、0Hz~数100kHzの帯域成分を有する電圧として出力されます。このうち入力信号の周波数の情報は位相検波器出力の直流付近に存在しますので、狭帯域のローパスフィルタ(吹出しⅡ)で抜き取ってVCXOの制御電圧VCとします。この結果PLLは入力信号の周波数には同期するように動作しますが、入力信号の瞬時位相変動には追従しなくなり、結果として位相雑音(ジッタ)が抑圧されたサイン波が得られることになります。ローパスフィルタの通過帯域幅が狭いほどVCXOの位相雑音の上昇量は抑制できる事になります。

4. PLLシンセサイザ

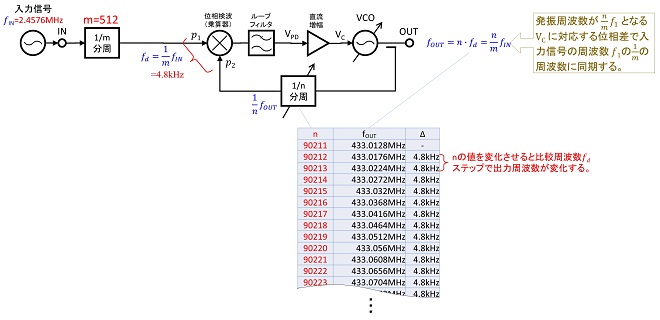

この回路は無線通信機でLO(局部発振回路)として最も多用されるアプリケーションです。1個の基準クロック(正確な基準周波数信号)から、無線送受信に必要となる様々な周波数のサイン波を合成するための基本手段として用いられます。図4に周波数を生成する原理、図6に周波数軸で見た動作の概要を示します。

(1) 周波数を生成する仕組み

無線通信では割り当てられた周波数帯域を等間隔に分割して「通信チャネル」として使用します。従って無線通信機の局部発振回路は「通信チャネル」の周波数間隔で多くの周波数を生成する必要が生じます。これを実現する為には図4に示すようにPLLの比較周波数𝑓dをチャネル間隔の周波数とし、図2で解説した「周波数を逓倍する仕組み」を用いて逓倍を行います。

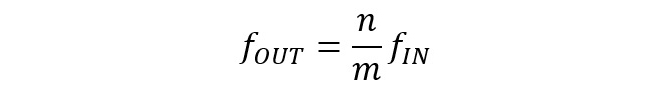

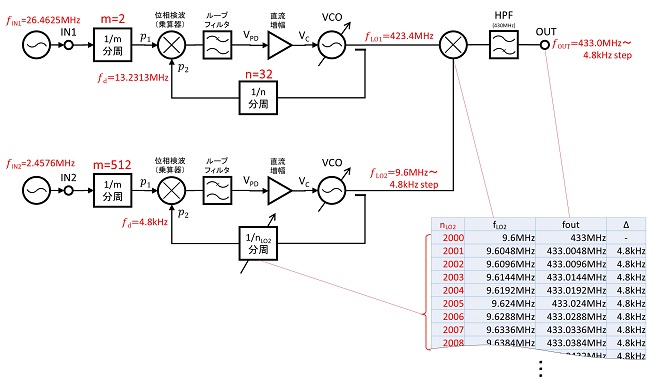

図4では基準クロック信号: 𝑓1=2.4576MHz、チャネル周波数間隔: 𝑓d=4.8kHzで、433MHz帯の無線通信で使用するキャリア信号を生成する事を想定した例です。周波数ステップ4.8kHzで出力周波数を変化させるためには、PLLの比較周波数: 𝑓dを4.8kHzにする必要があるので、入力された基準クロックは基準分周器(mカウンタ、もしくはRカウンタと呼ばれます)で1/512に分周されて位相検波回路(乗算器)に入力されます。これを分周フィードバック型のPLLで逓倍するわけですが、図4の例では90211+n倍(n=0,1,2,3・・・)に逓倍しています。結果的にこのタイプのPLLの入力周波数: 𝑓Iと出力周波数: 𝑓OUTは(式4-1)に示す関係になります。

(式4-1)

実際には逓倍数が90000倍にもなるとPLLがロックしていてもVCOの位相は大きく揺らいでしまう※2ので、いきなり433MHzまで逓倍せずに別の周波数と掛け算してアップコンバートするなどの手法が多用されます(図5)。

図5 430MHzから4.8kHz間隔で周波数を可変にする例

※2: フィードバック回路に分周器を挿入した場合、VCOと基準信号の位相差は、位相検波器で検出した位相差の分周数倍になります。つまりフィードバック分周器の分周数n=90000で、位相検波器入力における基準信号とフィードバック信号(VCOの分周された信号)の位相差が1°あった場合、VCO端では90000°(250サイクル)の位相差になっています。つまり周波数シンセサイザの場合、PLLといえども位相同期の精度を厳密に保証するのは技術的に難しくなります。

(2) PLLシンセサイザの位相雑音

さて、位相雑音の話が登場したところで、PLLシンセサイザの位相雑音について、図6を用いて解説します。

PLLを周波数シンセサイザとして使用する場合、VCOには広い発振周波数範囲が要求されるため、LCオシレータ(クラップ発振回路)など、周波数可変範囲の広い発振回路を適用し、ループフィルタの通過帯域幅は極力広く設計します。このPLLは2章に記載した「VCOの位相雑音レベルよりも、入力信号の位相雑音レベルが小さい」ケースに該当し、VCOの位相雑音レベルが入力信号に位相同期することで、抑制される・・・ つまり3章のPLLフィルタと補正する側、される側が逆転したような動作になります。周波数軸上で見ると、PLLの入力には図5の吹出しⅠに示すような位相雑音の小さいサイン波が基準信号として入力され、位相比較器(乗算器)でVCOの出力するサイン波(吹出しⅢ)と位相比較(同一周波数の乗算)されます。PLLフィルタの時と同様、両者とも純粋なサイン波ではなくある帯域幅を持った波形なので、両者の積(差周波成分)は直流のみにはならず、0Hz~数100kHzの帯域成分を有する電圧として出力されます。PLLシンセサイザでは、この帯域成分を極力すべてVCOにフィードバックすることによりVCOの瞬時位相変動を抑制し、位相雑音(ジッタ)が抑圧された、異なる周波数のサイン波が得られることになります(図5の吹出しⅢ)。当然、直流成分もフィードバックされているので、逓倍されたサイン波の周波数偏差も入力の基準信号と同一になります。

5. 第14話のまとめ

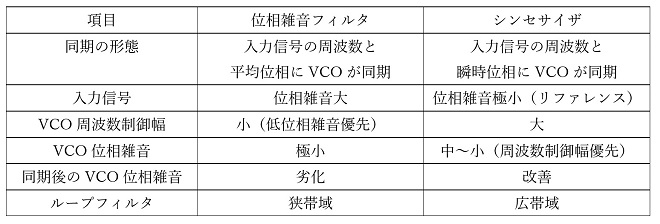

第14話ではPLLとは具体的にどういうものかをご紹介し、通信機器における代表的アプリケーションの「位相雑音フィルタ」と「周波数シンセサイザ」について解説しました。同じPLLでも、両者で位相同期の考え方が異なっており、これに合わせてループフィルタに要求される特性が異なります。改めて表1に整理しておきます。

表1 PLLの用途と設計の違い

今回は話を簡単にするために省略しましたが、PLLシンセサイザには分周回路が挿入されるため、位相比較器に入力される信号はサイン波ではなく矩形波になります。またVCOの発振周波数範囲が広いため、位相検波の範囲も±90°の範囲ではあっという間に位相検波可能な範囲を逸脱してしまい、初期引き込みに失敗する可能性があります。従って一般的なPLLシンセサイザにおいてはフリップフロップを用いた「位相・周波数検波回路(PFD)」なるものが適用されます。次回はこのあたりを解説したいと考えます。

今更聞けない無線と回路設計の話 バックナンバー

- 【テーマ2】デシベルと無線工学 (第19話) レベルダイヤグラムの縦軸(その3)

- 【テーマ2】デシベルと無線工学 (第18話) レベルダイヤグラムの縦軸(その2)

- 【テーマ2】デシベルと無線工学 (第17話) レベルダイヤグラムの縦軸(その1)

- 【テーマ2】デシベルと無線工学 (第16話) レベルダイヤグラムの構成

- 【テーマ2】デシベルと無線工学 (第15話) 非線形歪み(その5)

- 【テーマ2】デシベルと無線工学 (第14話) 非線形歪み(その4)

- 【テーマ2】デシベルと無線工学 (第13話) 非線形歪み(その3)

- 【テーマ2】デシベルと無線工学 (第12話) 非線形歪み(その2)

- 【テーマ2】デシベルと無線工学 (第11話) 非線形歪み(その1)

- 【テーマ2】デシベルと無線工学 (第10話) 線形歪み(フェージング現象)

- 【テーマ2】デシベルと無線工学 (第9話) 足される雑音と掛けられる雑音

- 【テーマ2】デシベルと無線工学 (第8話) 等価雑音の内訳

- 【テーマ2】デシベルと無線工学 (第7話) 無線通信の成立条件(その3)

- 【テーマ2】デシベルと無線工学 (第6話) 無線通信の成立条件(その2)

- 【テーマ2】デシベルと無線工学 (第5話) 無線通信の成立条件

- 【テーマ2】デシベルと無線工学 (第4話) dBmとdBµVの複雑な関係

- 【テーマ2】デシベルと無線工学 (第3話) dB(デシベル)を知る(その2)

- 【テーマ2】デシベルと無線工学 (第2話) dB(デシベル)を知る(その1)

- 【テーマ2】デシベルと無線工学 (第1話) (プロローグ)無線通信機の天井と床

- 【テーマ1】三角関数のかけ算と無線工学 (第30話) 三角関数のかけ算と無線工学の切っても切れない深い縁

- 【テーマ1】三角関数のかけ算と無線工学 (第29話) 交流ベクトル空間と直交ミキサ(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第28話) 交流ベクトル空間と直交ミキサ(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第27話) 交流ベクトル空間と直交ミキサ(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第26話) 交流ベクトル空間と直交ミキサ

- 【テーマ1】三角関数のかけ算と無線工学 (第25話) マイナスの周波数

- 【テーマ1】三角関数のかけ算と無線工学 (第24話) 同一周波数のサイン波の掛け算と周波数の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第23話) 同一周波数のサイン波の掛け算と周波数の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第22話) 同一周波数のサイン波の掛け算と周波数の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第21話) ループフィルタとPLLの応答特性の話(その6)

- 【テーマ1】三角関数のかけ算と無線工学 (第20話) ループフィルタとPLLの応答特性の話(その5)

- 【テーマ1】三角関数のかけ算と無線工学 (第19話) ループフィルタとPLLの応答特性の話(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第18話) ループフィルタとPLLの応答特性の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第17話) ループフィルタとPLLの応答特性の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第16話) ループフィルタとPLLの応答特性の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第15話) 位相検波器の話

- 【テーマ1】三角関数のかけ算と無線工学 (第14話) PLLの動作原理と代表構成

- 【テーマ1】三角関数のかけ算と無線工学 (第13話) PLLの役割とサイン波の純度について

- 【テーマ1】三角関数のかけ算と無線工学 (第12話) 同一周波数のサイン波のかけ算と位相のはなし

- 【テーマ1】三角関数のかけ算と無線工学 (第11話) ギルバートセル乗算器(その3・ギルバートセル乗算回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第10話) ギルバートセル乗算器(その2・定電流源とカレントミラー回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第9話) ギルバートセル乗算器(その1・差動増幅の基礎)

- 【テーマ1】三角関数のかけ算と無線工学 (第8話) ダブルバランスドミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第7話) ダブルバランスドミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第6話) トランジスタミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第5話) トランジスタミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第4話) 非線形動作を利用したかけ算のまとめ

- 【テーマ1】三角関数のかけ算と無線工学 (第3話) ミキサの線形性って何?

- 【テーマ1】三角関数のかけ算と無線工学 (第2話) 周波数変換とミキサ(混合)回路

- 【テーマ1】三角関数のかけ算と無線工学 (第1話) サイン波のかけ算

外部リンク

アマチュア無線関連機関/団体

各総合通信局/総合通信事務所

アマチュア無線機器メーカー(JAIA会員)