Mr. Smithとインピーダンスマッチングの話

【第32話】 低雑音増幅器(LNA)のインピーダンスマッチング(その7・LNAの設計(後編))

第31話ではNFマッチとパワーマッチ(S11に対する共役整合)の中間を狙った整合回路を設計したものの、単方向利得GTUがデバイスの最大安定利得MSGを超えてしまい、発振リスクが生じてしまいました。第32話は発振リスク解消の為の入力整合回路の再設計からスタートします。

1. 入力整合回路の再々設計

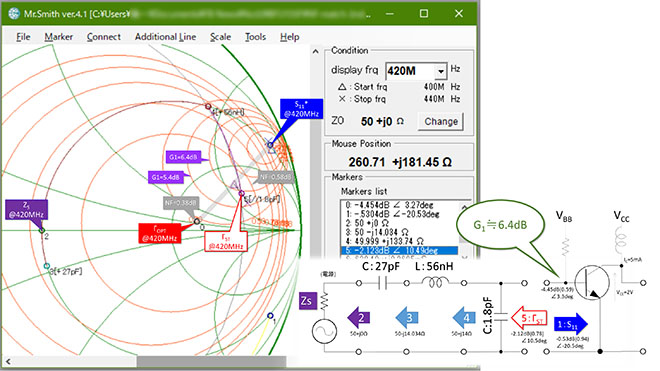

図1は第31話の図8の再掲です。左側のチャートで、デバイスから見た信号源インピーダンスがG1≧6.4dBの等利得円よりもS11*に近づくと右側のチャートに示すようにS22’が1以上になる事が判明しました。この領域では後段の反射係数が大きいと発振する可能性が生じます。負荷インピーダンスがピタリ50Ωなら問題は生じないのですが、実用性を考慮して今回は入力整合回路を信号源インピーダンスをG1=6.4dBの等利得円の外側に変換する設計にすることとします。

図1 BFU725Fの信号源インピーダンスと出力インピーダンスの関係

第31話では入力VSWRを下げるため、図1の左側のチャートに示すように、信号源インピーダンスを極力S11*に近づけましたが、この結果デバイスの出力インピーダンスは右側のチャートの1番マーカの位置となりました。入力のVSWRを大きくすることは本意ではないので、出力反射係数が1以下になるギリギリのところに信号源インピーダンスを持って行く方針とし、左のチャートの赤い太線で示したようにG1=6.4dBの等利得円の外側ギリギリを狙って入力整合回路を設計することにします。結果を図2に示します。

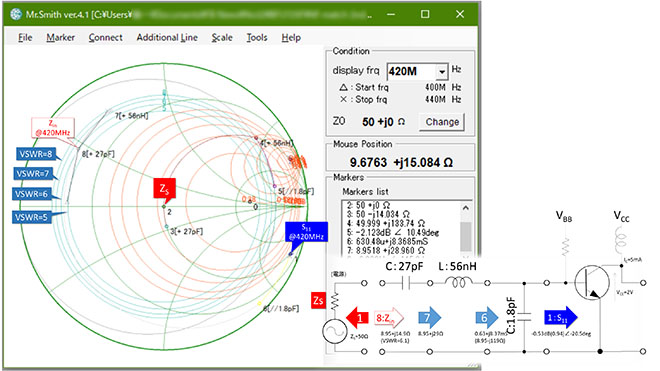

これで概ね、狙い通りの信号源インピーダンスになっていると考えます。次にこの増幅器の入力インピーダンスを確認します。入力インピーダンスはデバイスS11をスタート点として、入力整合回路を入力端子に向かって計算することで確認します。

図3に示すように、入力端子のVSWRは6.1となってしまいました。ΓOPTに整合させたときのVSWR>10よりはマシという状況ですが、今回はこの設計に止める事とします。

なかなか八方美人の設計結果が得られませんでしたが、ここから先の選択肢は概ね以下のうちのどれかになります。

(1) アンテナなどのように信号源インピーダンスが実態のある値で、かつVSWR=6.1であっても動作不安定にならない場合

→入力整合回路は今回の設計を採用する。(回路コスト、設計難易度共に小さくなる)

(2) 回路の入力インピーダンスを極力50Ωとすることが要求される場合

→入力にアイソレータを挿入、アイソレータの挿入損失分だけNFは劣化するため、入力整合回路を一番最初の設計(NFマッチ→第28話の図8)とする。

(3) NFも入力VSWRももっと改善したい場合

→中和回路を設けてS12を改善し、その状態で取得したSパラメータを使用して再設計する。

2. 出力インピーダンスの確認

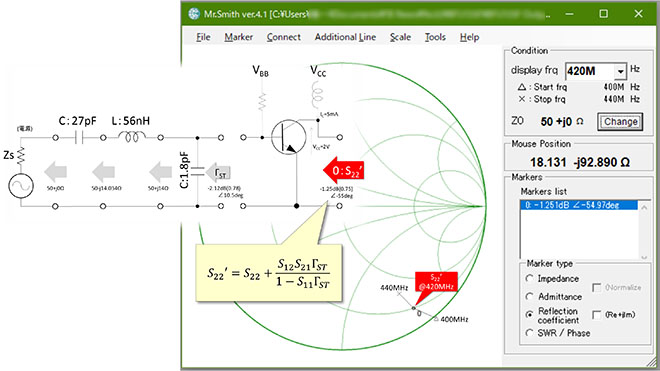

改めて入力の整合回路が決まったので、この時のデバイスの出力インピーダンスS22'がスミスチャートの内側に収まっている事を確認します。S22'は第17話の(式2-4)(→図4に再掲)を用いて算出できます。結果を図4に示します。

図4は、Mr.Smith※1で計算した400MHz,420MHz,440MHzの3周波数のΓST(図2の5番マーカの値)と、各周波数のSパラメータを用い、Microsoft® Excel®で計算した結果を再度Mr.Smithにプロットしたものです。400MHzの値が微妙にスミスチャートの外側領域に飛び出していますが、S22’は概ね狙ったところにいると判断します。

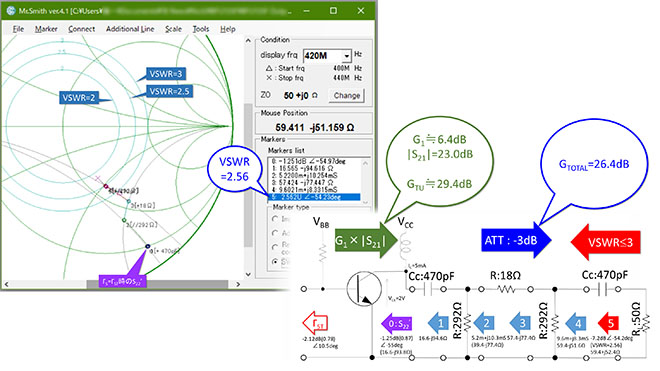

3. 利得の確認と出力回路の設計

第31話で決めた整合設計方針では、出力はインピーダンスマッチングを行わずに50Ω負荷で終端するのですが、図4に示す出力インピーダンスのままではVSWR≒14であり、第24話~第25話で解説した「段間のインピーダンスが定まらない」問題が発生します。後段回路の事を考慮すると非常に使いにくいので、第25話で解説したアッテネータを挿入して緩衝する方法を採用します。設計結果を図5に示します。

入力整合回路の再々設計の結果、G1は約6.4dBです(図2)。出力側は整合をとらず、トランジスタの負荷インピーダンスを50ΩとしたのでG2=0dBです。従ってデバイス出力端での単方向利得GTUは

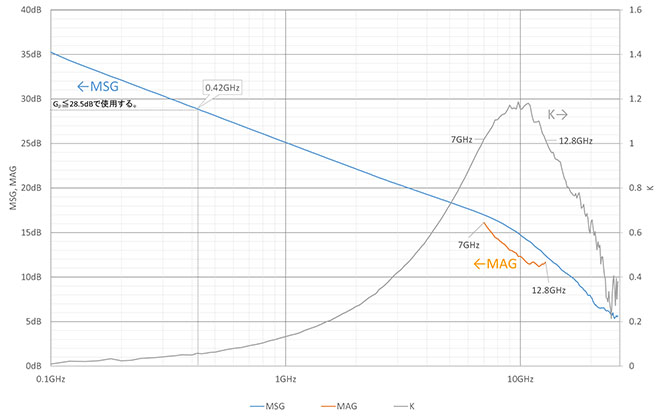

となり、第31話で計算したMSG(図6)を少し超えるレベルとなります。プロの立場で設計再現性、環境安定性、ならびに経年安定性を考慮するなら、もう少し利得を下げて使いたいところですが、ここではデバイス性能をできるだけ引き出す事として、この結果を採用します。

出力に3dBのアッテネータが挿入されるので、出力端子における利得は26.4dB、VSWRは2.6となります。トランジスタとアッテネータを接続するための結合キャパシタCCは、リアクタンスが設計誤差の要因になるので、キャパシタンスが大きい方が良いのですが、徒にキャパシタンスを大きくすると自己共振周波数が動作周波数にかかってくる可能性があるので、420MHzで|XC|≦1Ωを目安に470pFとしました。

図6 BFU725FのMSG/MAG/K (第31話の図7から再掲。計算方法は第19話参照)

4. 直流設計

最後に直流設計を行って回路を完成させます。BUF725Fはバイポーラトランジスタなので、何らかフィードバック型のバイアス回路を採用しないと熱暴走のリスクがあります。高周波増幅器では共通端子に素子を挿入すると不安定になりやすい(第18話の図8を参照)傾向があるので、電源電圧VCCを今回採用した動作点VCE=2Vよりも高い電圧に設定して、電圧帰還型のバイアス回路を適用します。電圧帰還型バイアス回路では、VCEに対してVCCが高いほど強い帰還がかかり熱安定性が良くなります。しかし徒に電圧を高くすると、電源電圧利用率の大幅な低下(=効率低下)を招き、またゼロバイアスになった時にコレクタ-エミッタ間をブレークダウンさせるリスクも発生するため、トランジスタのVCEO(MAX)以下の電圧とすべきです。

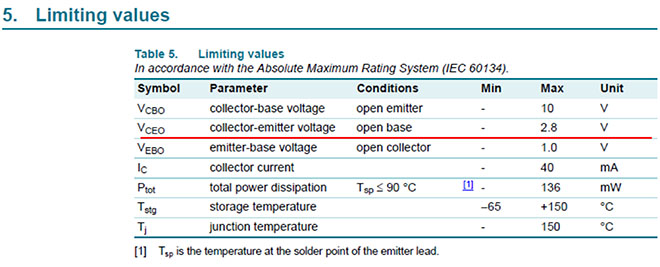

メーカのデータシート(図7)によると、BUF725FのVCEO(MAX)は2.8Vです。VCE=2Vで使用するのであれば、VCC≧3V、できれば5Vくらいで使用したいところですが、バイアス回路がオープンになった瞬間にブレークダウンしてしまうリスクがあるので、今回はVCC=2.5Vとし、緩いフィードバック(動作点は温度で変動するが熱暴走は防ぐ)で使用することにします。

図7 BUF725FのVCEO(MAX) (赤線で示した項、NXP社データシートから抜粋)

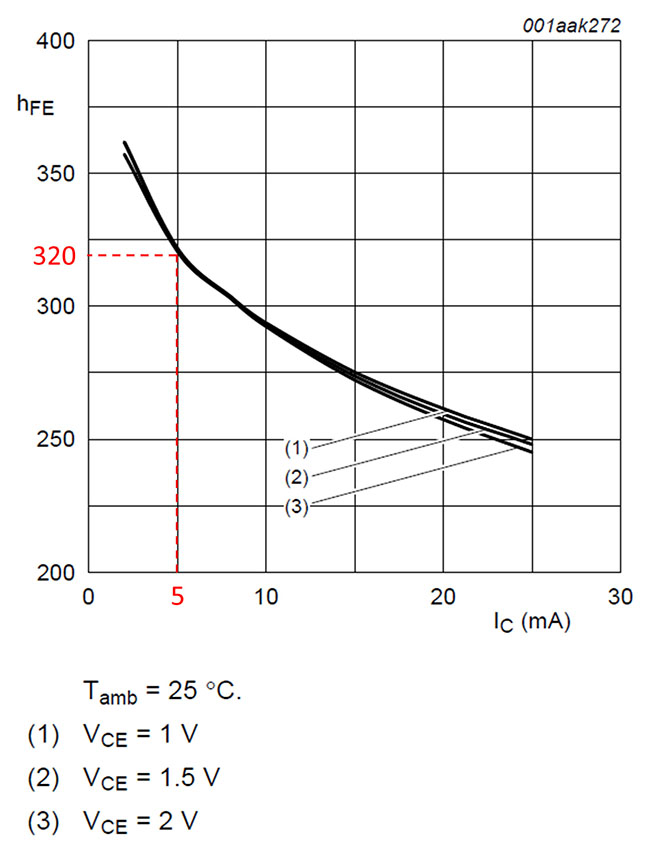

また直流電流増幅率は動作点のIC=5mAにおいては約320と読み取れます(図8)ので、これらの条件で電圧帰還型の直流バイアス回路を設計します。

図8 BUF725FのIC vs. hFE特性 (NXP社データシートから抜粋)

設計結果を図9に示します。CC,Cp,RFCの値は目安です。RFCは自己共振周波数が800MHz程度、直流抵抗1Ω以下の条件でCoilcraft社の製品を調べて選定しましたが、負荷抵抗50Ωに対するインダクタンスとしては不足気味で、できるだけ大きい値とすることが望ましいと考えます。Cpの選択基準はコレクタの直流等価抵抗、RFCのリアクタンスなどを勘案して、CCと同程度の値で良いと考えます。実際にはトランジスタの動作帯域が広いので、帯域外の特性に配慮しながら帯域外のインピーダンスがあまり上昇しないよう、複数の容量のキャパシタを接続することも考慮する必要があるかもしれません。

今回の設計では、入力のVSWRをこれ以上悪くしたくないという考えで、トランジスタの出力インピーダンスがほぼ全反射(やや負性抵抗)の条件で動作させています。このため実際に試作すると、コレクタ側の反射の影響で発振する可能性が残ります。試作した回路が発振傾向を示す場合は、コレクタに直列抵抗を挿入するなどの発振止めが必要になる可能性があります。

5. 第32話のまとめ

ようやく低雑音増幅器の解説を終えることができました。いざ解説を始めると、細かい話がいっぱいあって、何処まで判りやすくお伝えできたか少々不安に思っていますが、以上で増幅回路の整合設計について一通りのお話ができたと考えています。

今回の設計例のように、増幅器などにおいては、入出力に「整合回路」が存在するにも関わらず、意外と共役整合させていないというのが実態です。増幅回路の設計においては、このような「トランスインピーダンス(インピーダンス変換)」回路も含めて「整合回路」と呼ばれており、駆け出しのエンジニアを翻弄させていると思います。

第31話のまとめとダブりますが、低雑音増幅器の設計手順を要約すると以下の通りです。

(1) Stability circleを作成し、入出力のマッチングコンセプトを決める。

(2) 入力整合回路のゴールとなる信号源インピーダンスを決めて整合回路を設計する。

(3) 設計結果を基に入力VSWRを評価する。

(4) 単方向利得GTUを評価しMSGを超えていないか確認する。同様にトランジスタの出力インピーダンスS22’も負性抵抗領域に入っていないか確認する。

(5) コレクタに装荷させるインピーダンスを決めて(今回は50Ωでした)、負荷インピーダンスをその値に変換する。

(6) 設計結果を基に出力VSWRを評価し、必要に応じてアッテネータによるインピーダンスの確定を図る。

(7) 直流バイアス回路を設計する。

なお(7)は本来なら、動作点を決めた段階で最初に実施する手順です。この手順でバイアス回路と整合回路の組み合わせ方を確立し、その上で整合回路を設計する事になります。今回はNFマッチを解説するのが主目的でしたので後付けの解説になってしまいました。

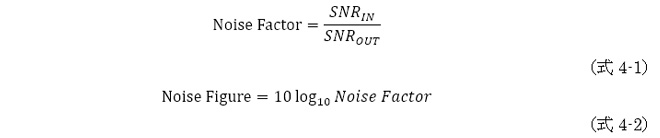

最後に、LNAの話を締めくくるに際し雑音指数の英語表記について少し触れておきます。日本語の教科書・専門書では「NF:雑音指数」と表記されるのですが、英文の教科書、専門書ではNFは Noise FactorとNoise Figureの2種類があり、下記の通り使い分けされています。

つまりNoise Factorが真数値でNoise FigureがdB値を示します。両者を区別するため、真数値NoiseFactorの記号をFと表記する場合もあるようです。日本の文献では、あまり両者を区別していないので、真数のFに該当するのか、dB値のNFに該当するのかは読み手が判断する必要があるので注意が必要です。(本稿でも区別していません)

次回からは増幅器を離れ、アンテナのインピーダンスを中心にお話します。

※1 Mr.Smith ver4.1のダウンロードはこちらから

https://www.vector.co.jp/soft/winnt/business/se521255.html

※2 本連載に掲載した設計例は、あくまで設計の考え方を示すものであり、実際に製作して性能を検証したものではありません。掲載した設計結果を、読者の方が二次利用されて発生する如何なる結果に対しても、筆者、ならびに月刊FB News編集部は一切の責任を負いません。

Mr. Smithとインピーダンスマッチングの話 バックナンバー

- 【第40話】 (連載最終話) インピーダンスマッチングの四方山話

- 【第39話】 アンテナと空間のインピーダンス(その6 平衡と不平衡(その2))

- 【第38話】 アンテナと空間のインピーダンス(その6 平衡と不平衡(その1))

- 【第37話】 アンテナと空間のインピーダンス(その5 放射抵抗と給電抵抗)

- 【第36話】 アンテナと空間のインピーダンス(その4 アンテナの放射抵抗)

- 【第35話】 アンテナと空間のインピーダンス(その3 放射電力と空間のインピーダンス)

- 【第34話】 アンテナと空間のインピーダンス(その2 ダイポールアンテナ)

- 【第33話】 アンテナと空間のインピーダンス(その1 電磁波とは何か)

- 【第32話】 低雑音増幅器(LNA)のインピーダンスマッチング(その7・LNAの設計(後編))

- 【第31話】 低雑音増幅器(LNA)のインピーダンスマッチング(その6・LNAの設計 (前編))

- 【第30話】 低雑音増幅器(LNA)のインピーダンスマッチング(その5・定NF円)

- 【第29話】 低雑音増幅器(LNA)のインピーダンスマッチング(その4・ノイズパラメータ)

- 【第28話】 低雑音増幅器(LNA)のインピーダンスマッチング(その3・NFマッチ)

- 【第27話】 低雑音増幅器(LNA)のインピーダンスマッチング(その2・NFとSN比)

- 【第26話】 低雑音増幅器(LNA)のインピーダンスマッチング(その1・雑音とは何か)

- 【第25話】 そのインピーダンス、本当に存在しますか? (その2)

- 【第24話】 そのインピーダンス、本当に存在しますか? (その1)

- 【第23話】 トランジスタの利得とミスマッチの関係

- 【第22話】 トランジスタの出力インピーダンスと負荷インピーダンス

- 【第21話】 S12と付き合う(その3)

- 【第20話】 S12と付き合う(その2)

- 【第19話】 S12と付き合う(その1)

- 【第18話】 S12の正体

- 【第17話】 増幅器とSパラメータ(その2)

- 【第16話】 増幅器とSパラメータ(その1)

- 【第15話】 Qとは何か(その3)

- 【第14話】 Qとは何か(その2)

- 【第13話】 Qとは何か(その1)

- 【第12話】 λ/4線路の共振と分布定数回路(その2)

- 【第11話】 λ/4線路の共振と分布定数回路(その1)

- 【第10話】 Sパラメータの基礎

- 【第9話】 直列共振と並列共振 その2

- 【第8話】 直列共振と並列共振

- 【第7話】 スミスチャートは日本人の発明?

- 【第6話】 スミスチャートとは何か(その2)

- 【第5話】 伝送線路と反射係数(その2)

- 【第4話】 伝送線路と反射係数

- 【第3話】 スミスチャートとは何か(その1)

- 【第2話】 インピーダンスマッチングの方法

- 【第1話】 なぜインピーダンスマッチング?

お知らせ

-

2022.11.15

11月号後半の記事をアップしました

-

2022.11.1

11月号の記事をアップしました

-

2022.10.17

10月号後半の記事をアップしました

-

2022.10.3

10月号の記事をアップしました

-

2022.9.15

9月号後半の記事をアップしました

-

2022.9.1

9月号の記事をアップしました

-

2022.8.15

8月号後半の記事をアップしました

-

2022.8.1

8月号の記事をアップしました

-

2022.7.15

7月号後半の記事をアップしました

-

2022.7.1

7月号の記事をアップしました

-

2022.6.15

6月号後半の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JL3ZGL」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2022.6.1

6月号の記事をアップしました

6月4日(土)、JH1CBX/3が14MHz SSBに初オンエアします。 入感がありましたらぜひお声がけください。 -

2022.5.16

5月号後半の記事をアップしました

-

2022.5.2

5月号の記事をアップしました

5月14日(土)、JL3ZGLはオペレーターにMasacoさんを迎えHAMtte交信パーティに 参加します。詳しくは4月号のニュースをご確認ください。 -

2022.4.15

4月号後半の記事をアップしました

-

2022.4.1

4月号の記事をアップしました

-

2022.3.15

3月号後半の記事をアップしました

-

2022.3.1

3月号の記事をアップしました

-

2022.2.15

2月号後半の記事をアップしました

-

2022.2.1

2月号の記事をアップしました

-

2022.1.17

1月号後半の記事をアップしました

-

2022.1.5

1月号の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JA3YUA」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2021.12.15

12月号後半の記事をアップしました

-

2021.12.1

12月号の記事をアップしました

-

2021.11.15

11月号後半の記事をアップしました

-

2021.11.01

2021年11月号の記事をアップしました

-

2021.10.15

10月号後半の記事をアップしました

-

2021.10.01

2021年10月号の記事をアップしました

-

2021.09.15

9月号後半の記事をアップしました

-

2021.09.01

2021年9月号の記事をアップしました

-

2021.08.16

8月号後半の記事をアップしました

-

2021.08.02

2021年8月号の記事をアップしました

-

2021.07.15

7月号後半の記事をアップしました

-

2021.07.01

2021年7月号の記事をアップしました

-

2021.06.15

6月号後半の記事をアップしました

-

2021.06.01

2021年6月号の記事をアップしました

-

2021.05.17

5月号後半の記事をアップしました

-

2021.05.06

2021年5月号の記事をアップしました

-

2021.04.15

4月号後半の記事をアップしました

-

2021.04.01

2021年4月号の記事をアップしました

連載記事 Masacoの「むせんのせかい」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.15

3月号後半の記事をアップしました

連載記事「今月のハム」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.01

2021年3月号の記事をアップしました

-

2021.02.15

2月号後半の記事をアップしました

-

2021.02.01

2021年2月号の記事をアップしました

-

2021.01.15

1月号後半の記事をアップしました

-

2021.01.05

2021年1月号の記事をアップしました

-

2020.12.15

12月号後半の記事をアップしました

-

2020.12.01

2020年12月号の記事をアップしました

-

2020.11.16

11月号後半の記事をアップしました

-

2020.11.02

2020年11月号の記事をアップしました

-

2020.10.15

10月号後半の記事をアップしました

-

2020.10.01

2020年10月号の記事をアップしました

-

2020.09.15

9月号後半の記事をアップしました

-

2020.09.01

2020年9月号の記事をアップしました

-

2020.08.17

8月号後半の記事をアップしました

-

2020.08.03

2020年8月号の記事をアップしました

-

2020.07.15

7月号後半の記事をアップしました

-

2020.07.01

2020年7月号の記事をアップしました

-

2020.06.15

6月号後半の記事をアップしました

-

2020.06.01

2020年6月号の記事をアップしました

-

2020.05.01

2020年5月号の記事をアップしました

-

2020.04.15

4月号後半の記事をアップしました

-

2020.04.01

2020年4月号の記事をアップしました

-

2020.03.16

3月号後半の記事をアップしました

-

2020.03.09

JARD、eラーニングでのアマチュア無線国家資格取得を呼び掛けるお知らせを、臨時休校で自宅待機中の小中高生に向けて発表。詳しくはこちら。

-

2020.03.02

2020年3月号の記事をアップしました

-

2020.02.17

2月号後半の記事をアップしました

-

2020.02.03

2020年2月号の記事をアップしました

-

2020.01.15

1月号後半の記事をアップしました

-

2020.01.06

2020年1月号の記事をアップしました

-

2019.12.16

12月号後半の記事をアップしました

-

2019.12.02

2019年12月号の記事をアップしました

-

2019.11.15

11月号後半の記事をアップしました

-

2019.11.01

2019年11月号の記事をアップしました

-

2019.10.15

10月号後半の記事をアップしました

-

2019.10.01

2019年10月号の記事をアップしました

-

2019.09.17

9月号後半の記事をアップしました

-

2019.09.02

2019年9月号の記事をアップしました

-

2019.08.16

8月号後半の記事をアップしました

-

2019.08.01

2019年8月号の記事をアップしました

-

2019.07.16

7月号後半の記事をアップしました

-

2019.07.01

2019年7月号の記事をアップしました

-

2019.06.17

6月号後半の記事をアップしました

-

2019.06.01

2019年6月号の記事をアップしました

-

2019.05.20

5月号後半の記事をアップしました

-

2019.05.07

2019年5月号の記事をアップしました

-

2019.04.15

4月号後半の記事をアップしました

-

2019.04.01

2019年4月号の記事をアップしました

-

2019.03.15

3月号後半の記事をアップしました

-

2019.03.01

2019年3月号の記事をアップしました

-

2019.02.15

2月号後半の記事をアップしました

-

2019.02.01

2019年2月号の記事をアップしました

-

2019.01.18

1月号後半の記事をアップしました

-

2019.01.07

2019年1月号の記事をアップしました

-

2018.12.17

12月号後半の記事をアップしました

-

2018.12.01

2018年12月号の記事をアップしました

-

2018.11.15

11月号後半の記事をアップしました

-

2018.11.01

2018年11月号の記事をアップしました

-

2018.10.15

10月号後半の記事をアップしました

-

2018.10.01

2018年10月号の記事をアップしました

-

2018.09.15

9月号後半の記事をアップしました

-

2018.09.01

2018年9月号の記事をアップしました

-

2018.08.17

8月号後半の記事をアップしました

-

2018.08.01

2018年8月号の記事をアップしました

-

2018.07.17

7月号後半の記事をアップしました

-

2018.07.02

2018年7月号の記事をアップしました

-

2018.06.15

6月号後半の記事をアップしました

-

2018.06.01

2018年6月号の記事をアップしました

-

2018.05.15

5月号後半の記事をアップしました

-

2018.05.01

2018年5月号の記事をアップしました

-

2018.04.16

4月号後半の記事をアップしました

-

2018.04.02

2018年4月号の記事をアップしました

-

2018.03.15

3月号後半の記事をアップしました

-

2018.03.01

2018年3月号の記事をアップしました

-

2018.02.15

2月号後半の記事をアップしました

-

2018.02.01

2018年2月号の記事をアップしました

-

2018.01.15

1月号後半の記事をアップしました

-

2018.01.05

2018年1月号の記事をアップしました

-

2017.12.15

12月号後半の記事をアップしました

-

2017.12.1

12月号をアップしました

-

2017.11.15

11月号後半の記事をアップしました

-

2017.11.1

11月号をアップしました

-

2017.10.16

10月号後半の記事をアップしました

-

2017.10.2

10月号をアップしました

-

2017.9.15

What a healthy time! ~健康を応援する特別なお料理~/第3回 食物繊維たっぷり! 海藻の和風リゾット、FB Monthly Fashion/第9回 秋っぽい柄&色コーデ、子供の無線教室/第9回 「アンテナの形や大きさに注目!!」を掲載しました

-

2017.9.4

<速報>ハムフェア2017を掲載しました

-

2017.9.1

9月号をアップしました

-

2017.8.17

What a healthy time! ~健康を応援する特別なお料理~/第2回 和風のポトフ 納豆ソース添え、FB Monthly Fashion/第8回 夏のお出かけコーデ、子供の無線教室/第8回 「無線機にはどんなものがあるの?」を掲載しました

-

2017.8.1

8月号をアップしました

-

2017.7.18

What a healthy time! ~健康を応援する特別なお料理~/第1回 メロンの冷製スープ ナッツのアイスクリームのせ、FB Monthly Fashion/第7回 コットンTシャツコーデとボーイズコーデ、子供の無線教室/第7回 「電波はどうやって海外や宇宙に届くの?」を掲載しました

-

2017.7.1

7月号をアップしました

-

2017.6.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第9回 FB Girlsの野望 with ムースと甘エビのタルタル、FB Monthly Fashion/第6回 雨の日コーデと親子コーデ、子供の無線教室/第6回 「電波はいろいろなところで大活躍!!」を掲載しました

-

2017.6.1

6月号をアップしました

-

2017.5.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第8回 番外編 春うらら♪豪華弁当でお花見、FB Monthly Fashion/第5回 ブラウス&シャツを使ったコーディネート、子供の無線教室/第5回 「周波数によって変わる、電波の特徴」を掲載しました

-

2017.5.1

5月号をアップしました

-

2017.4.17

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第7回 ARDFの思い出 with 2種類のソースのカルボナーラ、FB Monthly Fashion/第4回 Gジャンを使ったコーディネート、子供の無線教室/第4回 「電波の性質を覚えよう」を掲載しました

-

2017.4.1

4月号をアップしました

-

2017.3.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第6回 初めてのQSOの思い出 with グリーンのアクアパッツァ、FB Monthly Fashion/第3回 ピンクを使ったコーディネート、子供の無線教室/第3回 「電波はどうやって伝わるの?」を掲載しました

-

2017.3.1

3月号をアップしました

-

2017.2.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第5回 FB Girlsの試験の思い出 withウマ辛和風スープ、FB Monthly Fashion/第2回 デニムと明るめニットのコーディネートを掲載しました

-

2017.2.1

2月号をアップしました

-

2017.1.16

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第4回 YLハムを増やす秘策とは?! withおなかにやさしいお料理、【新連載】FB Monthly Fashion/第1回 アウター別おすすめコーディネート(ライダース・ノーカラー・ダッフル)を掲載しました

-

2017.1.5

1月号をアップしました

-

2016.12.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第3回 YLハムの行く年来る年 with ブイヤベースの洋風お鍋を掲載しました

-

2016.12.1

12月号をアップしました

-

2016.11.15

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(後編)!、What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第2回 YLハムの悩み解決!with サケのフレンチトーストを掲載しました

-

2016.11.1

11月号をアップしました

-

2016.10.17

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(前編)!、【新連載】What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第1回 FB GirlsのプライベートQSO with 土瓶蒸しのリゾットを掲載しました

外部リンク

アマチュア無線関連機関/団体

各総合通信局/総合通信事務所

アマチュア無線機器メーカー(JAIA会員)

次号は 12月 1日(木) に公開予定